Abstract

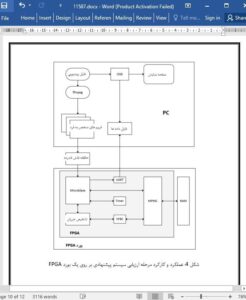

Machine vision algorithms provide significant benefits for Lab-on-Chip (LoC) systems by automating the experimental process. This paper presents an FPGA-based machine vision flow detection implementation for microfluidic Lab-on-Chip (LoC) experiments. We propose and implement a novel architecture that exploits modern FPGA parallelism capabilities and makes efficient use of device resources to achieve real-time data collection in megapixel resolutions, at rates exceeding 30000 frames per second.

I. INTRODUCTION

MICROFLUIDIC Labs-on-Chip offer significant advantages to clinical diagnostics by bringing the benefits of miniaturization and automation and enabling the execution of complicated biological experiments in an integrated environment at the Point-of-Care (PoC). Control of biological fluids through motion detection, often makes use of point sensors (light barrier, electromechanical, etc.), which have several disadvantages like reduced measurement resolution, limited information capabilities and higher cost. In recent years, various research groups have used machine vision solutions for information extraction and actuator control, which offer significant benefits compared to previous approaches, like increased precision and real-time response.

VI. CONCLUSION

In this paper, an FPGA-based machine vision flow detection system for microfluidic Lab-on-Chip experiments, was proposed and implemented, supporting multiple simultaneous high-speed fluids, a first to our knowledge in relevant literature. An implementation test setup was designed to evaluate the performance and functionality of the system on an XUPV5 FPGA development board, using a Virtex-5 FPGA device. The obtained results clearly demonstrate the high speed detection capabilities and robustness of the system, with frame rates approaching and exceeding 30kfps for common parameter sets, providing significant performance and automation advantages to molecular diagnostics applications. The small area footprint and minimal on-chip memory utilization, provide adequate space for larger systems to be implemented on the same chip.