# Nanodiamond Vacuum Field Emission Integrated Differential Amplifier

Shao-Hua Hsu, Weng Poo Kang, *Member, IEEE*, Jimmy L. Davidson, *Senior Member, IEEE*, Jin H. Huang, and David V. Kerns, Jr., *Fellow, IEEE*

Abstract—The development of a novel vacuum differential amplifier (diff-amp) array employing vertically configured nanodiamond (ND) vacuum field emission transistors (ND-VFETs) on a single chip is presented. The diff-amp array is composed of a common ND emitter array integrated with partition gates and split anodes. An identical pair of ND-VFETs with wellmatched field emission transistor characteristics was fabricated by using a dual-mask well-controlled microfabrication process, involving a mold-transfer self-aligned gate-emitter technique in conjunction with ND deposition into the micropatterned molds in the active layer of a silicon-on-insulator substrate followed by gate partitioning to form diff-amp array. The ND-VFETs show gate-controlled modulation of emission with distinct cutoff, linear, and saturation regions. Signal amplification characteristics of the ND-VFET diff-amp are presented. A large common-moderejection ratio (CMRR) of 54.6 dB was measured for the diff-amp. The variation of CMRR performance with transconductance was examined, and the results were found to agree with the equivalent circuit model analysis. The accomplishment of this basic circuit building block, consisting of an integrated diff-amp, demonstrates the feasibility of using vacuum integrated circuits for practical applications, including high-radiation and temperature-tolerant space electronics.

Index Terms—Differential amplifier (diff-amp), integrated circuits (ICs), nanodiamond (ND), transistor, vacuum field emission (VFE).

#### I. INTRODUCTION

ACUUM FIELD EMISSION (VFE) microelectronics, relying on ballistic electron transport in vacuum, promises for high operation speed, low energy loss, and temperature and radiation immunity performance [1], [2]. Vacuum microelectronic devices are favorable for a variety of applications ranging from sensors and field emission displays to high-performance integrated circuits (ICs). VFE devices possess better noise immunity than solid-state devices and thereby can operate at

Manuscript received September 11, 2012; revised October 25, 2012; accepted November 9, 2012. Date of publication December 7, 2012; date of current version December 19, 2012. The review of this paper was arranged by Editor M. Thumm.

- S.-H. Hsu, W. P. Kang, and J. L. Davidson are with the Department of Electrical Engineering and Computer Science, Vanderbilt University, Nashville, TN 37235 USA (e-mail: weng.p.kang@vanderbilt.edu).

- J. H. Huang is with National Tsing Hua University, Hsinchu 300, Taiwan (e-mail: jihhuang@mx.nthu.edu.tw).

- D. V. Kerns, Jr., is with the Franklin W. Olin College of Engineering, Needham, MA 02492 USA.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2228485

a much lower current with good noise rejection performance. VFE integrated devices and circuits are good for high-speed and high-power applications and in harsh environments including high temperature and high radiation. In the past, only few practical implementations of VFE devices at circuit level have been reported even though the concepts and modeling of vacuum ICs were described [3], [4]. Improvement in VFE device stability, particularly cathode reliability, is required for the practical implementation of vacuum microelectronic devices in ICs.

Recent development of carbon-derived materials such as nanodiamond (ND) film and carbon nanotubes has revealed their superior electron field emission characteristics [5]–[16]. ND possesses the unique properties of low electron affinity, thermal stability, and mechanical hardness, making it a robust cathode material for VFE devices [6], [7]. In addition, n-type conductivity can be achieved by  $in\ situ$  nitrogen doping in chemical-vapor-deposited (CVD) ND film, concomitantly providing a deliberate amount of  $sp^2$  graphitic inclusion in the  $sp^3$  diamond matrix with enhanced electron emission characteristics [8], [9]. Moreover, the small grain size and smooth surface morphology of ND allow compatible integration with silicon microfabrication and thus further facilitate the development of vacuum microelectronics via the mold-transfer self-aligned gate—emitter technique [17].

VFE transistors (VFETs) utilizing CVD ND as the emitters with low threshold voltage, stable emission current, and high voltage gain have been reported [10]-[12], allowing their further implementations into vacuum ICs and logic gates. A realistic approach to demonstrate IC capability is the implementation of a differential amplifier (diff-amp), which is known to be the most important circuit building block used in analog and mixedsignal circuits of solid-state microelectronics. For instance, the input stage of an operational amplifier and the basic element of emitter-coupled high-speed logic [18], [19] incorporate the diff-amp. Our group created a VFE diff-amp based on carbonnanotube emitters in 2009 [16]. Recently, we have developed highly reliable nitrogen-incorporated ND cathodes for VFE devices [9]–[15] and have considered their deployment in vacuum ICs [20]. In this paper, the fabrication processes, dc field emission, and ac amplification characteristics of an ND-VFET diff-amp are presented. The advantage of better noise rejection was demonstrated by choosing to operate the device at low current. The device performance including the common-moderejection ratio (CMRR), an important figure of merit for diffamp, has been evaluated by experimental measurement. The

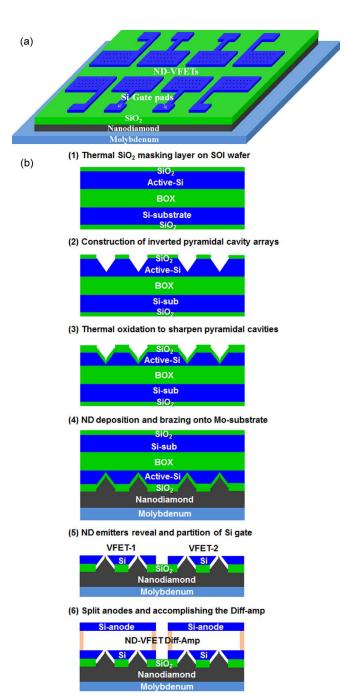

Fig. 1. (a) Schematic diagram of the ND-VFET diff-amp array chip with separate contact pads. The chip is brazed onto a Mo substrate. (b) Fabrication flowchart of the ND-VFET diff-amp.

equivalent circuit analysis based on dc characteristics has also been performed to analyze the CMRR value. The successful implementation of the ND-VFET diff-amp demonstrates the feasibility of using vacuum ICs as an alternative electronic circuit for harsh environment operation.

## II. FABRICATION OF ND VACUUM DIFF-AMP

Fig. 1 shows the schematic layout and fabrication scheme of the ND-VFET diff-amps on a chip. The IC chip consisting of an array of ND-VFETs, each has  $80 \times 80$  ND emitter tips, was fabricated by a simple dual-mask photolithography process on a

silicon-on-insulator (SOI) substrate using a mold-transfer selfaligned gate-emitter technique. The high-conductivity active silicon layer of the SOI was used as the mold as well as the gate layer. Inverted pyramidal molds were first constructed on the active silicon layer by photolithography patterning followed by silicon anisotropic wet etching [17]. The resulting mold layer was later used in the self-aligned gate structure. Next, a  $1-\mu$ m-thick SiO<sub>2</sub> was thermally grown on the inverted silicon pyramidal mold cavities to form the dielectric isolation between the gate and emitter electrodes and simultaneously produce an ultrasharp apex at the inverted pyramidal mold tips as the deposited ND conforms to achieve the tips or the emitters. Subsequently, nitrogen-incorporated ND was deposited into and on the molds by plasma-enhanced chemical vapor deposition using a gas mixture of CH<sub>4</sub>/H<sub>2</sub>/N<sub>2</sub>, automatically selfaligning the ND emitters to the silicon gate. The ND-filled mold was then coated with a composite layer of sputtered titanium and nickel to form the back contact and brazed onto a molybdenum substrate using a titanium-copper-silver (ticusil) brazing alloy. The Ti/Ni bilayer provided strong metallurgical adhesion with ND and facilitated the brazing of diamond onto the Mo substrate, while the ticusil layer provided good metal contact between ND and Mo substrate after being melted at 900 °C in vacuum of 10<sup>-7</sup> torr and solidified upon cooling. After etch removal of the silicon substrate and the buried oxide layer of the SOI, ultrasharp ND pyramidal cathodes with selfaligned Si gates were revealed by a thin down process of the active silicon layer in a HF/HNO<sub>3</sub> (1:30 volume ratio) mixture followed by partial etch of the thermal SiO<sub>2</sub> around the ND tips. This silicon thin down process was well controlled, providing uniform gate openings and the optimized proximity of gate to emitters. Then, a second lithographic patterning and silicon reactive ion etching was executed to partition the Si gate and form individual ND-VFETs with separate contact pads for diff-amp implementation. Finally, the diff-amp was realized by mounting two highly conductive silicon anodes adjacently and above a selected pair of identical ND-VFETs forming a split anode with 600- $\mu$ m spacing above the gate electrodes.

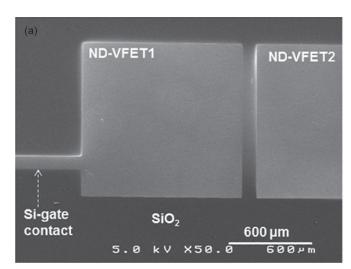

The fabricated adjacent ND-VFETs examined under scanning electron microscope (SEM) are shown in Fig. 2(a). Fig. 2(b) shows part of the ND-VFET and higher magnifications. A single ND cathode with an ultrasharp apex and a self-aligned Si gate surrounding it is displayed in the inset. When examined under high magnification, the ND-VFET exhibited similar gate-to-cathode spacing of  $\sim 1~\mu m$  and uniform ND tip sharpness, with more than 90% yield. Uniform gate-to-cathode spacing with well-formed ND cathodes is crucial to acquiring an identical transistor pair with well-matched electrical characteristics for practical diff-amp implementation.

#### III. CHARACTERIZATION AND MODELING OF DIFF-AMP

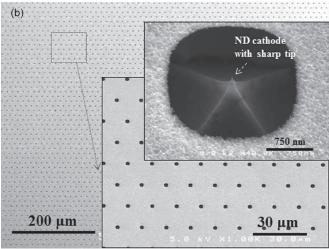

Fig. 3 shows the schematic test setup for characterizing the ND-VFET diff-amps. The fabricated ND-VFE devices on the chip were placed in a vacuum chamber maintained at  $10^{-7}$  torr and tested separately for dc field emission in order to evaluate the matching transistor pair's characteristics. For each ND-VFET, positive gate voltage  $(V_q)$  was applied on the gate

Fig. 2. (a) Top-viewed SEM image of a pair of ND-VFETs. (b) SEM micrographs showing part of the ND-VFET. Insets show higher magnification and a single ND cathode with self-aligned Si gate.

Fig. 3. Schematic diagram of the testing circuitry for the ND-VFET diffamp in common–emitter configuration. DC bias voltages were applied to operate the pair of transistors in saturation mode. AC input small signals were applied through coupling capacitors to gate electrodes, while output voltages are collected at anode electrodes.

electrode with a given anode voltage  $(V_a)$  such that electrons induced from cathodes by  $V_g$  were gathered by anode electrodes. The anode and gate currents  $(I_a \ {\rm and} \ I_g)$  were measured as a function of  $V_g$  by a downward voltage sweep method to characterize each transistor pair in the saturation mode. Two ND-VFETs with nearly identical field emission features were then utilized for diff-amp ac testing.

The ac signal amplification of the ND-VFET diff-amp was examined by feeding input signals to the gate electrodes and recording the output signals at the anode electrodes of the transistors, biased at a predetermined operating point in the saturation region [12], as shown by the schematic diagram in Fig. 3. We defined the input and output voltages of ND-VFETs to be  $v_{\rm in1}$  and  $v_{\rm out1}$  for transistor 1 and  $v_{\rm in2}$  and  $v_{\rm out2}$  for transistor 2.

For common-mode operation, both ND-VFETs amplified the same input sinusoidal signals and created a differential output voltage between anode electrodes. The input and output voltages of the diff-amp in common mode are denoted by  $v_{\rm ic}$  and  $v_{\rm oc}$ , respectively, where  $v_{\rm ic}$  is equal to  $v_{\rm in1}$  and  $v_{\rm in2}$  whereas  $v_{\rm oc}$  is equal to  $v_{\rm out1}-v_{\rm out2}$ . Thus, the common-mode voltage gain  $A_{\rm cm}$  is equal to  $v_{\rm oc}/v_{\rm ic}$ . Using the equivalent circuit analysis [18], [21], it can be expressed as

$$A_{\rm cm} = \frac{(I_{a1} - I_{a2}) \times (R_a / / R_L)}{v_{\rm ic}} = \frac{\Delta I_a}{V_{\rm ic}} \times (R_a / / R_L)$$

(1)

where  $R_a$  is the anode resistance,  $R_L$  is the load resistance, and  $\Delta I_a$  is the mismatch value of anode emission currents.

For differential-mode measurement, the sinusoidal small signal was first applied only to the gate electrode of transistor 1 of the diff-amp, while no signal was fed to the gate terminal of transistor 2 to achieve a half-circuit differential input, i.e.,  $v_{\rm in1} = V_p \, \sin(2\pi ft)$  V, where  $V_p$  and f are the amplitude and frequency of the input signal, and  $v_{\rm in2} = 0$  V. The differential input and output voltages ( $v_{\rm id} = v_{\rm in1} - v_{\rm in2}$  and  $v_{\rm od} = v_{\rm out1} - v_{\rm out2}$ ) were then equal to the input and output voltages of transistor 1 since there was no signal amplified by transistor 2, i.e.,  $v_{\rm id} = v_{\rm in1}$  and  $v_{\rm od} = v_{\rm out1}$ . Therefore, the half-circuit differential-mode voltage gain  $A_{\rm dm1}$  of the diff-amp is equal to the voltage gain of the transistor 1 [18], [21] which can be described as

$$A_{\rm dm1} = \frac{v_{\rm out1}}{v_{\rm in1}} = \frac{I_{a1} \times (R_a//R_L)}{V_{\rm in1}} = g_{m1} \times (R_a//R_L).$$

(2)

In this analysis, the internal parasitic capacitances were ignored since we examine low-frequency response to demonstrate the operation of ND-VFE diff-amp, and the coupling capacitors were chosen to be at the microfarad level such that their reactance was negligible.

Next, the same procedures were employed on transistor 2 with no signal applied on transistor 1. Similar differential-mode voltage gain  $A_{\rm dm2}$  can be obtained from (2), but it will be  $180^{\circ}$  out of phase.

Finally, the value of CMRR was determined by CMRR =  $|A_{\rm dm}/A_{\rm cm}|$ . This value was utilized to evaluate the ability of a diff-amp to reject input noise common to both input terminals,

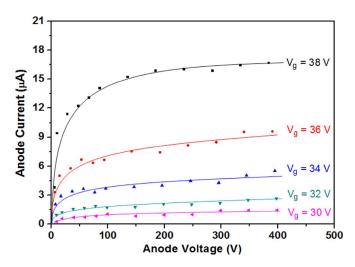

Fig. 4. Plots of the anode current versus anode voltage of the fabricated ND-VFET at various gate voltages, showing clear transistor characteristics with distinct cutoff, linear, and saturation regions.

particularly important when the signal of interest is contained in the voltage difference of inputs. Larger  $g_m$  and smaller  $\Delta I_a$  obviously would enhance the CMRR of a diff-amp.

The transconductance  $(g_m)$  of the ND-VFET, defining the variation of  $I_a$  with the change of  $V_g$  at fixed  $V_a$  bias, was determined from the dc characteristics as described by

$$g_m = \frac{\partial I_a}{\partial V_g}\bigg|_{v_a = \text{const}}.$$

(3)

The  $g_m$  determines the current driving capability and voltage gain of the transistor. It also plays an important role in diffamp performance since the differential-mode voltage gain is determined by the voltage gain of a single transistor which is governed by  $g_m$ .

# IV. ELECTRICAL PERFORMANCE OF DIFF-AMP

Fig. 4 shows a family of  $I_a$ – $V_a$ – $V_g$  transistor characteristics of an ND-VFET, where distinct cutoff, linear, and saturation regions are observed. The anode current increased with anode voltage as  $V_a$  was less than 100 V and saturated at  $V_a$  above  $\sim$ 100 V for a fixed gate bias. This feature is consistent with the electron transport mechanism discussed previously [12]. The device exhibited a high amplification factor of  $\sim$ 215 at a constant anode current of  $\sim$ 9.5  $\mu$ A, demonstrating a high dc voltage gain appropriate for amplifier applications. The relatively low current, compared to that in diode configuration [9], is due to the gate screening effect and the significant decrease in geometrical field enhancement factor attributed to the triode's construction. Nevertheless, higher  $I_a$  can be achieved at higher gate voltages.

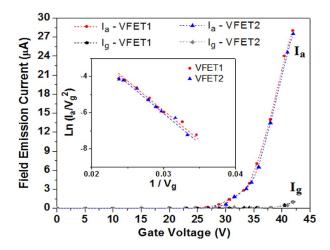

The electron field emission characteristics of ND-VFETs were measured and compared in order to find a close-matched transistor pair for diff-amp testing. Fig. 5 shows the  $I_a$ - $V_g$  curves of the VFET pair, operated in the saturation region at  $V_a = 350$  V, along with corresponding gate currents. The exponential increase features of anode currents with the gate

Fig. 5. DC field emission characteristics of an ND-VFET pair used for diffamp at fixed  $V_a=350~\rm V$  exhibit well-matched anode currents as a function of gate voltage with negligible gate currents. (Inset) F–N plots of the corresponding  $I_a$ – $V_g$  data.

voltage are indicative of the gate-induced field emission nature, obeying the Fowler–Nordheim (F–N) equation [22]

$$I = \frac{k_1 A \beta^2 V_g^2}{\phi d^2} \exp\left[\frac{-k_2 \phi^{1.5} d}{\beta V_q}\right] \tag{4}$$

where  $k_1$  and  $k_2$  are constants, A is the emitting area,  $\beta$  is the field enhancement factor,  $\Phi$  is the work function of the emitting surface, and d is the gate-to-emitter spacing.

In addition, the linearly negative slope of  $\ln(I_a/V_g^2)$ -versus- $1/V_g$  plots extracted from the corresponding  $I_a$ - $V_g$  data, as shown in the inset, is consistent with the F–N relationship in (4), further confirming that the anode currents are due to the field-enhanced emission behavior. These two VFETs possessed well-matched emission anode currents up to  $\sim$ 28  $\mu$ A at  $V_g$  of 42 V with a mismatch of 1.2% and fairly low gate turn-on voltages, defined as the voltage required to draw 1- $\mu$ A emission current, of  $\sim$ 29 and  $\sim$ 30 V, respectively. Such nearly identical characteristics of the transistor pair would provide useful common-mode-rejection performance in the diff-amp. The VFETs also exhibited negligible gate intercepted currents,  $\sim$ 3.5% of  $I_a$ , suggesting the long-term operation capability and stability of the diff-amp.

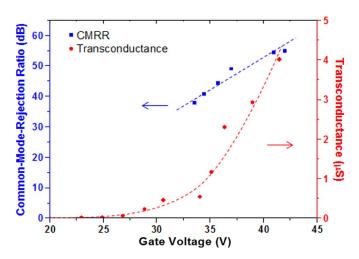

Based on the recorded  $I_a$ – $V_g$  values, the  $g_m$  was computed and plotted as a function of  $V_g$  at fixed  $V_a = 350$  V, as shown in Fig. 6. The exponentially increasing trend was observed in the  $g_m$ -versus- $V_g$  plot, demonstrating that the anode emission current was strongly affected by the gate voltage, governed by [23], [24]

$$g_m = \frac{k_1 A \beta}{\phi d} \left( \frac{2\beta}{d} V_g + k_2 \phi^{1.5} \right) \exp \left[ -\frac{k_2 \phi^{1.5} d}{\beta V_q} \right]. \tag{5}$$

The  $g_m$  was determined to be  $\sim 4~\mu S$  at  $V_g = 42~V$ , a reasonable choice for our diff-amp operation, and the value agrees with our previous results obtained from another ND-VFET at the same anode current [12]. Higher  $g_m$  is expected at higher operation voltages and currents due to the exponential relationship between  $g_m$  and  $V_g$ . Furthermore, the emission current driving ability by gate voltage of VFETs will

Fig. 6. Plots of the transconductance and measured CMRR versus the gate voltage of the fabricated ND-VFET pair at a given anode voltage ( $V_a=350~{

m V}$ ).

be further improved by employing a smaller gate-to-cathode distance. The effect of  $g_m$  on common-mode-rejection performance of the diff-amp will be discussed later in this section.

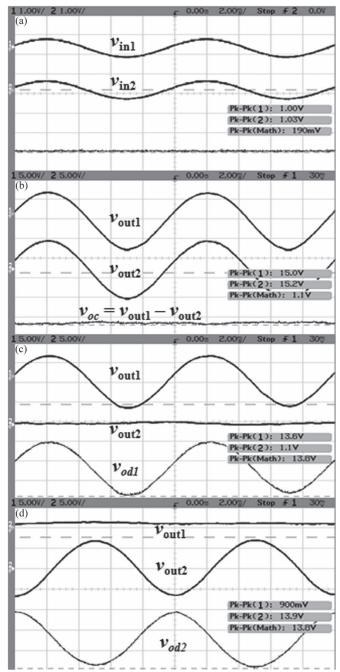

After acquiring dc characteristics, the ac signal amplification performance of the ND-VFET diff-amp was measured at a predetermined operation point in the saturation region. An ac sinusoidal input signal with an amplitude of 0.5 V at 100 Hz was superimposed on  $V_g=42$  V at the gate terminals, and the amplified output signals were recorded across the load resistors  $R_a//R_L$  (10 M $\Omega$  each) at the anode electrodes by a digital oscilloscope. The differential output voltage  $(v_{\rm out1}-v_{\rm out2})$  was obtained by using the built-in math function of the digital oscilloscope. In the common-mode test, the same small signals, as shown in Fig. 7(a), were applied to both of the inputs, and the signals were amplified to 15.0 and 15.2 V at outputs 1 and 2, respectively, as shown in Fig. 7(b), resulting in a small peak-to-peak common-mode output voltage  $v_{\rm oc}$  of  $\sim$ 1.1 V and a calculated  $A_{\rm cm}$  of  $\sim$ 0.0256, based on (1).

On the other hand, in the differential-mode tests, the small signal was first imposed on the first input of the diff-amp, while no signal was applied to the other input, i.e.,  $v_{\rm in1} =$  $0.5 \sin(2\pi ft)$  V and  $v_{\rm in2} = 0 \sin(2\pi ft)$  V. Fig. 7(c) shows the corresponding output waveforms with a differential output voltage  $v_{\rm od1}$  of  ${\sim}13.8$  V, giving a proper voltage gain at the operating current of 28  $\mu$ A. Similarly, by alternating the input sequence, the output waveform of transistor 2  $v_{\rm out2}$  and the corresponding differential output signal  $v_{\rm od2}$  with an  $\sim$ 13.8-V peak-to-peak value and a 180° phase shift are shown in Fig. 7(d) as the input signal amplified only by the second transistor. The  $A_{\rm dm}$  was computed to be  $\sim 13.8$  which is equivalent to the voltage gain of a single-ended transistor amplifier. Then, the CMRR of the ND-VFET diff-amp was determined to be  $\sim$ 540 (54.6 dB), demonstrating the feasibility for vacuum IC implementation. Relatively less noise was observed on  $v_{\rm od1}$  and  $v_{\rm od2}$ waveforms compared to  $v_{\rm oc}$ , implying that the noise common to both input terminals was offset in the differential-mode outputs, a basic and required feature of a diff-amp. Note that a doubled CMRR of  $\sim$ 1080 (60.7 dB) can be obtained under the condition of fully differential signals applied to the input terminals. This

Fig. 7. AC characteristics of the single-chip ND-VFET diff-amp: (a) Input signals to both gate terminals in common mode, (b) common-mode output signals recorded at both anode electrodes, (c) first differential-mode output waveforms, and (d) second differential-mode output waveforms with 180° phase shift

value is comparable to that of the commercially available solidstate diff-amps which are well known to have limited operating temperature range [25]. Therefore, the fabricated ND-VFET diff-amp can be an alternative IC building block providing good common-mode-rejection performance with capability for harsh environment operation [13]–[15].

The ac measurement procedures were then repeated on the ND-VFET diff-amp for variant operation points, and the corresponding CMRR is plotted as a function of  $V_g$ , as shown in Fig. 6. The enhancement of CMRR with  $V_g$  from  $\sim 37.9$  dB at

33.5 V to  $\sim$ 54.6 dB at 42 V was observed, which is attributed to the increase of the  $g_m$  and transistor voltage gain, agreeing with the prediction of equivalent circuit analysis where

$$CMRR = \frac{v_{ic}g_m}{\Delta I_a}.$$

(6)

The CMRR in decibels increased linearly with the gate voltage because  $g_m$  is an exponential function of  $V_g$  as indicated in (5). The further improvement of common-mode rejection is potentially achievable by the improvement of the transconductance described earlier in this section and by minimizing the anode current mismatch. The high-frequency response of the ND-VFET diff-amp will be explored in the future with optimum device structure and better test setup.

Equations (1) and (2) were utilized to estimate the common-mode and differential-mode voltage gains of the ND-VFET diff-amp. In this experiment, the diff-amp was operated at  $V_g=42~\rm V$  with an ac input voltage amplitude of 0.5 V for  $R_a$  and  $R_L$  of 10 M $\Omega$  each. The  $A_{\rm cm}$  and  $A_{\rm dm}$  were calculated to be 0.039 and 20, respectively, giving an estimated CMRR of 513 (54.2 dB) which is consistent with the experimentally measured result. The slight overestimations of both  $A_{\rm cm}$  and  $A_{\rm dm}$  in the analysis model were observed, which are probably due to the neglect of the noninfinite output resistance looking into the anode. Nevertheless, the estimation of CMRR is reliable since the CMRR is independent of load and output resistances, providing a simple method to evaluate the common-mode-rejection performance of the VFE diff-amp.

### V. CONCLUSION

A basic circuit building block of ND-VFET diff-amp for vacuum IC has been developed and implemented. A dualmask microfabrication process involving the mold-transfer selfaligned gate-emitter technique coupled with ND deposition and gate partitioning has been employed for the fabrication of the ND-VFET pairs on a chip. The ND-VFET pair showed wellmatched field emission transistor characteristics with low gate turn-on voltage and negligible gate intercepted current. A large CMRR of  $\sim$ 540 (54.6 dB), which is consistent with the estimated value in the analysis model, was realized at an operating gate voltage of 42 V with a transconductance of 4  $\mu$ S. The enhancement of CMRR with increasing gate voltage as well as transconductance was observed, agreeing with the equivalent circuit analysis and suggesting that higher CMRR is achievable at higher operation voltage. The successful implementation of this basic circuit building block, consisting of an integrated VFET diff-amp, demonstrates the feasibility of using vacuumbased ICs for practical applications, including high-speed and temperature- and radiation-hardened electronics.

#### REFERENCES

- [1] I. Brodie, "Physical considerations in vacuum microelectronics devices," *IEEE Trans. Electron Devices*, vol. 36, no. 11, pp. 2641–2644, Nov. 1989.

- [2] I. Brodie and P. R. Schwoebel, "Vacuum microelectronic devices," *Proc. IEEE*, vol. 82, no. 7, pp. 1006–1034, Jul. 1994.

- [3] R. F. Greene, H. F. Gray, and G. Campsie, "Vacuum integrated circuits," in *Proc. IEEE IEDM*, 1985, pp. 172–175.

- [4] L. Zhang, A. Q. Gui, and W. N. Carr, "Lateral vacuum microelectronic logic gate design," *J. Micromech. Microeng.*, vol. 1, no. 2, pp. 126–134, Jun. 1991.

- [5] A. Wisitsora-at, W. P. Kang, J. L. Davidson, and D. V. Kerns, "A study of diamond field emission using micro-patterned monolithic diamond tips with different sp<sub>2</sub> contents," Appl. Phys. Lett., vol. 71, no. 23, pp. 3394– 3396, Dec. 1997.

- [6] J. van der Weide, Z. Zhang, P. K. Baumann, M. G. Wensell, J. Bernholc, and R. J. Nemanich, "Negative-electron-affinity effects on the diamond (100) surface," *Phys. Rev. B, Condens. Matter*, vol. 50, no. 8, pp. 5803–5806, Aug. 1994.

- [7] W. Zhu, G. P. Kochanski, and S. Jin, "Low-field electron emission from undoped nanostructured diamond," *Science*, vol. 282, no. 5393, pp. 1471– 1473, Nov. 1998.

- [8] S. Bhattacharyya, O. Auciello, J. Birrell, J. A. Carlisle, L. A. Curtiss, A. N. Goyette, D. M. Gruen, A. R. Krauss, J. Schlueter, A. Sumant, and P. Zapol, "Synthesis and characterization of highly-conducting nitrogendoped ultrananocrystalline diamond films," *Appl. Phys. Lett.*, vol. 79, no. 10, pp. 1441–1443, Sep. 2001.

- [9] K. Subramanian, W. P. Kang, J. L. Davidson, R. S. Takalkar, B. K. Choi, M. Howell, and D. V. Kerns, "Enhanced electron field emission from micropatterned pyramidal diamond tips incorporating CH<sub>4</sub>/H<sub>2</sub>/N<sub>2</sub> plasma-deposited nanodiamond," *Diamond Relat. Mater.*, vol. 15, no. 4–8, pp. 1126–1131, Apr.–Aug. 2006.

- [10] K. Subramanian, W. P. Kang, and J. L. Davidson, "A monolithic nanodiamond lateral field emission vacuum transistor," *IEEE Electron Device Lett.*, vol. 29, no. 11, pp. 1259–1261, Nov. 2008.

- [11] K. Subramanian, W. P. Kang, and J. L. Davidson, "Nanocrystalline diamond lateral vacuum microtriode," *Appl. Phys. Lett.*, vol. 93, no. 20, pp. 203511-1–203511-3, Nov. 2008.

- [12] S. H. Hsu, W. P. Kang, J. L. Davidson, J. H. Huang, and D. V. Kerns, "Performance characteristics of nanocrystalline diamond vacuum field emission transistor array," *J. Appl. Phys.*, vol. 111, no. 11, pp. 114502-1–114502-7, Jun. 2012.

- [13] W. P. Kang, J. L. Davidson, K. Subramanian, B. K. Choi, and K. F. Galloway, "Nanodiamond lateral VFEM technology for harsh environments," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 4, pp. 1061–1065, 2007.

- [14] J. L. Davidson, W. P. Kang, K. Subramanian, A. Holmes-Siedle, R. A. Reed, and K. F. Galloway, "Diamond electronic device behavior after high neutron fluence exposure," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 4, pp. 2225–2229, Aug. 2009.

- [15] K. Subramanian, W. P. Kang, J. L. Davidson, N. Ghosh, and K. F. Galloway, "A review of recent results on diamond vacuum lateral field emission device operation in radiation environments," *Microelectron. Eng.*, vol. 88, no. 9, pp. 2924–2929, Sep. 2011.

- [16] Y. M. Wong, W. P. Kang, J. L. Davidson, D. V. Kerns, Jr., J. H. Huang, and K. F. Galloway, "Characterization and CMRR modeling of a carbon-nanotube field-emission differential amplifier," *IEEE Trans. Electron Devices*, vol. 56, no. 5, pp. 738–743, May 2009.

- [17] W. P. Kang, J. L. Davidson, and D. V. Kerns Jr., "Mold method for forming vacuum field emitters and methods for forming diamond emitters," U. S. Patent 6 132 278, Oct. 17, 2000.

- [18] A. S. Sedra and K. C. Smith, Microelectronic Circuits, 4th ed. New York: Oxford Univ. Press, 1998.

- [19] J. S. Rieh, B. Jagannathan, D. R. Greenberg, M. Meghelli, A. Rylyakov, F. Guarin, Z. Yang, D. C. Ahlgren, G. Freeman, P. Cottrell, and D. Harame, "SiGe heterojunction bipolar transistors and circuits toward terahertz communication applications," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 10, pp. 2390–2408, Oct. 2004.

- [20] S. H. Hsu, W. P. Kang, S. Raina, J. L. Davidson, J. H. Huang, and D. V. Kerns, "Vacuum field emission integrated differential amplifier," in *Proc. 25th Int. Vacuum Nanoelectron. Conf.*, Jeju, Korea, Jul. 9–13, 2012, vol. P1-57, pp. 1–2.

- [21] D. A. Neamen, Electronic Circuit Analysis and Design, 2nd ed. New York: McGraw-Hill, 2001, pp. 639–648.

- [22] R. H. Fowler and L. Nordheim, "Electron emission in intense electric fields," in *Proc. Roy. Soc. London A*, 1928, vol. A119, pp. 173–181.

- [23] W. J. Orvis, C. F. McConaghy, D. R. Ciarlo, J. H. Yee, and E. W. Hee, "Modeling and fabricating micro-cavity integrated vacuum tubes," *IEEE Trans. Electron Devices*, vol. 36, no. 11, pp. 2651–2658, Nov. 1989.

- [24] A. Wisitsorat-at, "Micropatterned diamond vacuum field emission devices," Ph.D. dissertation, Dept. Elect. Eng., Vanderbilt Univ., Nashville, TN, 2002.

- [25] Differential Amplifiers Product List, Analog Devices, Inc. [Online]. Available: http://www.analog.com/en/specialty-amplifiers/differential-amplifiers/products/index.html

**Shao-Hua Hsu** received the M.S. degree from National Central University, Jhongli, Taiwan. Since 2009, he has been working toward the Ph.D. degree in the Department of Electrical Engineering and Computer Science, Vanderbilt University, Nashville, TN.

**Jin H. Huang** received the Ph.D. degree in electrical engineering from Rutgers University, Piscataway, NJ, in 1992.

She is currently a Professor with the Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu, Taiwan.

Weng Poo Kang (S'80–M'89) received the Ph.D. degree in electric engineering from Rutgers University, Piscataway, NJ.

He has been with the Department of Electrical Engineering and Computer Science, Vanderbilt University, Nashville, TN, where he is currently a Professor.

**David V. Kerns, Jr.** (M'71–SM'84–F'91) received the Ph.D. degree from Florida State University, Tallahassee, in 1971.

He has been a Distinguished Professor and the Founding Provost with Franklin W. Olin College of Engineering, Needham, MA.

**Jimmy L. Davidson** (SM'85) received the M.S. and Ph.D. degrees in material science from Columbia University, New York, NY.

Since 1989, he has been with Vanderbilt University, Nashville, TN, where he is currently a Professor Emeritus and a Research Professor.