# High Voltage Gain Quasi-SEPIC DC-DC Converter

Y. P. Siwakoti, *Member, IEEE*, A. Mostaan, A. Abdelhakim, *Student Member, IEEE*, P. Davari, *Member IEEE*, M. Soltani, *Senior Member, IEEE*, Md N. H. Khan, *Student Member, IEEE*, L. Li, *Senior Member, IEEE*, F. Blaabjerg, *Fellow, IEEE*

## **Authors Contact Information**

- Dr. Yam P. SIWAKOTI (*Corresponding Author*) Mailing Address: Faculty of Engineering and Information Technology, University of Technology Sydney, AUSTRALIA.

E-mail: yam.siwakoti@uts.edu.au

- Mr. Ali Mostaan, Iranian Central Oil Field Company (I.C.O.F.C), Tehran, IRAN. E-mail: ali\_8457@yahoo.com

- Mr. Ahmed Abdelhakim, University of Padova, Vicenza, ITALY. E-mail: ahmed.a.abdelrazek@ieee.org

- Dr. Pooya Davari, Aalborg University, Aalborg, DENMARK.

E-mail: pda@et.aau.dk

- 5) Dr. Mohsen Soltani, Aalborg University, Esbjerg, DENMARK. E-mail: sms@et.aau.dk

- Mr. Md Noman Habib Khan, University of Technology Sydney, AUSTRALIA.

E-mail: MdNomanHabib.Khan@student.uts.edu.au

- 7) Dr. Li Li, University of Technology Sydney, AUSTRALIA.E-mail: li.li@uts.edu.au

- Dr. Frede BLAABJERG, Aalborg University, Aalborg, DENMARK. E-mail: fbl@et.aau.dk

Abstract— This paper proposes a modified coupled-inductor SEPIC dc-dc converter for high voltage gain (2 < G < 10) applications. It utilizes the same components as the conventional SEPIC converter with an additional diode. The voltage stress on the switch is minimal, which helps the designer to select a low voltage and low R<sub>DS-on</sub> MOSFET, resulting in a reduction of cost, conduction and turn ON losses of the switch. Compared to equivalent topologies with similar voltage gain expression, the proposed topology uses lower component-count to achieve the same or even higher voltage gain. This helps to design a very compact and lightweight converter with higher power density and reliability. Operating performance, steady-state analysis and mathematical derivations of the proposed dc-dc converter have been demonstrated in the paper. Moreover, extension of the circuit for higher gain (G > 10) application is also introduced and discussed. Finally, the main features of the proposed converter have been verified through simulation and experimental results of a 400 W laboratory prototype. The efficiency is almost flat over a wide range of load with the highest measured efficiency of 96.2%, and the full-load efficiency is 95.2% at a voltage gain of 10.

*Index Terms*— Boost converter, coupled-inductor, dc-dc converter, flyback transformer, SEPIC converter, Switched-Mode Power Supply (SMPS)

## I. INTRODUCTION

High conversion gain dc-dc power converters have recently seen an increased demand in variety of power electronics applications. In fact, the main reasons behind this increased attention have three folds. Firstly, fast deployment of Renewable Energy (RE) based power systems has intensified the need for high conversion gain power converters. This is due to the low voltage generation inherent in most RE sources such as Photovoltaic (PV) modules and fuel-cells, where stepping up the low input voltage (e.g., 20 V - 40 V) to higher voltage levels (e.g., 200 V - 400 V) is required in order to have a properly function grid-forming or grid-feeding converter [1], [2]. Secondly, prevalence of applications demanding higher voltage levels for better performance, from few hundreds of Volts such as for Light Emitting Diode (LED) in lightning [3] up to few kilovolts in pulsed power applications [4]. Lastly, one of the most relevant is the possibility of distributing electrical energy more efficiently at higher dc voltage levels (e.g., 380 V-400 V or even higher). This is the case in applications such as telecommunication and dc power systems where electrical energy can be transferred with higher efficiency, reliability and power quality [5], [6].

Conventionally, the boost and buck-boost topologies can be employed in order to step-up the output voltage. However, practically achieving conversion gains of beyond six due to presence of parasitic elements is not feasible [2]. Moreover, operating at high duty cycles compromise the boost converter efficiency as small turn-off times which may incline Electromagnetic Interference (EMI) and ripple current levels, indicating a requirement for larger magnetic components [2], [7]. Another derivation of a buck-boost topology suitable for high voltage applications is the flyback converter [4], [8], [9]. Although this topology is well employed for high voltage applications with low parts count, it is only suitable for very low power levels (i.e., < 300 W). This is due to the high dc magnetization current requirement of its flyback transformer, which increases the size of the transformer and consequently the losses for higher power levels under continuous conduction mode operation [8].

From this standpoint, many research efforts have been devoted towards developing high voltage gain power converters without imposing extreme duty ratio. In general, the demanded performance can be obtained through utilizing coupled-inductor, switched inductors and switched capacitor cells [7], [10]-[16] and/or employing multi-cell configurations [4], [17]-[21]. All these attempts are made in order to overcome the existing technological limits (i.e., power switch breakdown voltage and limited power ratings) and to reach the required output voltage level with minimum duty ratio (i.e., obtaining better efficiency). However, in many practical situations, in order to obtain the required voltage gain and reduce voltage stress across the power switch many switched-cells are typically required. Furthermore, using an impedance network is also considered as another topological variant. The impedance network based power converters. known as Z-source, is initially proposed for dc-ac inverter operation [22], but it can be modified to operate as a high voltage gain dc-dc converter [23]. Recently, with the aim of reducing start-up inrush

current and improving the voltage gain of conventional Z-source converter, a variety of modified impedance networks have been introduced. These modifications can be summarized as switched inductor, extended boost, switched inductor quasi Z-source and enhanced boost [24]-[29]. While using the aforementioned topologies a high voltage gain with small duty cycle (D) is achievable, but the demerits of the aforementioned topologies are high parts counts (i.e., diodes, inductors and capacitors) and particularly the conduction of most diodes in (1-D) of the switching period, which lead to high power loss and low efficiency.

In spite of topological improvements, connecting two or more power converters in to multi-cell configurations is an alternative way to achieve a high conversion ratio. This can be obtained by series/parallel connection of power converter units [4], [9], cascaded cells [18]-[20] or multilevel approach [21]. With no doubt, multi-cell connection of power converters is an effective way to match the required power rating, voltage gain and reduce voltage stresses across the power switches, but high component count and lower efficiency may limit their performance. Thereby, it is preferable to first maximize the converter performance at the topology level before applying multi-cell connection. It is worth noting that obtaining high voltage gain, high efficiency and high power density at the same time are contradicting targets and a compromise is required to match specific application requirements. As a result designing a power converter with minimum number of components is always desirable. Low parts count can be a good design factor as it may lead to a cost-effective, simple, compact and efficient power converter.

Among aforementioned techniques, using coupled inductor is an effective technique to increase the voltage gain while avoiding high parts count [30], [31]. The main concept in this approach is to obtain the desirable voltage gain by increasing the coupled inductors turns ratio without including more components to the power converter. Therefore, the power loss may be lowered and consequently the efficiency can be improved. The coupled inductor technique associated with the SEPIC topology is introduced in [32]-[34]. Other variants of this converter with higher voltage gain ratio are presented in [35]-[39]. Generally, two main drawbacks can be identified in the introduced methods. Firstly, using two magnetic elements [32]-[37] and necessity of including extra diodes and capacitors cells to further extend the voltage ratio significantly impair the power density. Secondly, in order to mitigate the adverse effect of coupled-inductor leakage inductance, a snubber circuit is mandatory [40]. The presence of snubber circuit impose additional losses on the power converter. However, with suitable coupled-inductor design it is possible to minimize the leakage inductance and consequently the snubber circuit, which in return improves the system efficiency. In [41]- [42], high gain DC-DC converters, using taped inductor technique are introduced where their operations are very similar to converters using coupled inductor technique. However, without minimizing the leakage inductance effects and without using the low power loss snubber circuit, the voltage spike across the power switch is high and the efficiency is degraded. Step-up current-fed converters [43]-[45] with low input current ripple are appropriate solutions

in renewable energy applications, particularly in fuel cell systems. High efficiency is achieved in these converters using soft switching techniques. However, their complicated structures and using more than one active power switch make their controller system more complicated.

From the above discussions, the present work focuses on coupled-inductor method as a suitable candidate to obtain high voltage with low power losses in low to medium power applications. The proposed method is based on the SEPIC dc-dc converter topology. Here using a coupled-inductor, less number of components are employed comparing with prior-art methods. The voltage stress across the active power switch is minimized, which highlights the possibility of utilizing low voltage power switches (i.e., low switching losses) with low turn-on resistance (i.e., low conduction losses), which lead to an efficient and cost-effective design. Moreover, by improving the magnetic coupling the leakage inductance effect is minimized. The principle of operation, theoretical analysis of the proposed converter are investigated in comparison with its similar counterparts. The reported analysis is validated by key experimental results of a 400 W prototype. This paper is improved version of the conference paper [46]. In [46], this converter was introduced for very low power (5 W) applications as a front end DC-DC converter for piezoelectric systems and here are the following improvements for the current work:

- a) This converter is introduced as a high step-up and high efficiency converter in renewable energy application with nominal input voltage 40 V and output voltage 400 V as well as having considerable higher power (400 W).

- b) In addition to CCM mode, the converter is analyzed in the boundary conduction mode (BCM) and discontinuous conduction mode (DCM). Moreover, a design guideline in order to select the appropriate components value is added to this paper.

- A derivative converter with higher voltage gain (section IV) based on the proposed converter is also presented.

- d) In order to minimize the leakage inductance effects and prevent the voltage spike across the power switch, an improved magnetic coupling is designed and a RCD snubber circuit with low power loss is added in the experimental prototype as well as an efficiency measurement and loss distribution. A peak efficiency of 96.2% confirms the effectiveness of this converter in renewable energy applications.

This paper is structured as follows: Section II describes the proposed topology operation principle and design guidelines under steady state conditions. Analyzing the prior-art methods in comparison with the proposed topology through highlighting key aspects of their performance are addressed in Section III. Section IV is dedicated to further extend the proposed topology for higher voltage gain ratios. In Section V, experimental results are presented to substantiate the effective performance of the proposed method. Finally, conclusions are drawn in Section VI.

## II. OPERATING PRINCIPLE AND STEADY STATE ANALYSIS OF THE QUASI-SEPIC DC-DC CONVERTER

This section starts first by illustrating the operating principle of the proposed converter in continuous conduction mode (CCM). Then, its operation in the discontinuous conduction mode (DCM) is introduced, considering the critical case between the CCM and the DCM, which is called the boundary conduction mode (BCM). Finally, it shows the design steps or guidelines of a 400 W converter.

## A. CCM Operation

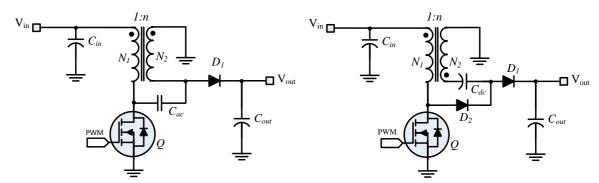

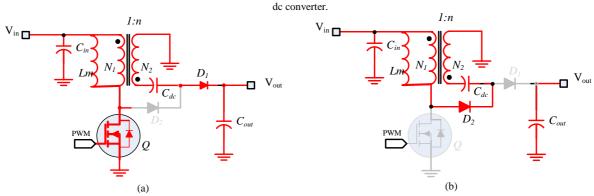

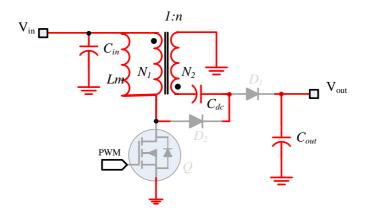

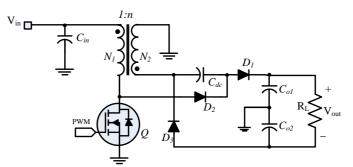

Compared to the basic coupled-inductor SEPIC converter, as shown in Fig. 1(a), the proposed converter, which is shown in Fig. 1(b), utilizes the same number of components with an additional diode. It is worth noting that this structure does not require an isolated gate drive circuitry for the employed MOSFET, resulting in lower cost and volume. Furthermore, a capacitor is connected in series with the transformer secondary winding, preventing the flow of the dc current in the transformer and, hence, avoiding saturation due to dc current.

Fig. 1. Circuit schematic showing (a) traditional coupled-inductor SEPIC dc-dc converter and (b) proposed coupled-inductor quasi-SEPIC dc-

Fig. 2. Equivalent circuits of the proposed converter in one switching cycle (a) Mode 1 (Q<sub>ON</sub>), and (b) Mode 2 (Q<sub>OFF</sub>).

In order to do further analysis on the converter operation, several assumptions are taken into account as follows:

1) The MOSFET and the diodes are ideal, i.e. the ON resistances of the MOSFET and voltage drop across the diodes are neglected;

2) All the employed capacitors are large enough, i.e. the voltage ripples across them are negligible; and

3) The leakage inductance of two coupled inductors are negligible and they are modeled as an ideal transformer with a turns ratio of  $N_1:N_2$  and a magnetizing inductance of  $L_m$ , parallel connected to the primary winding.

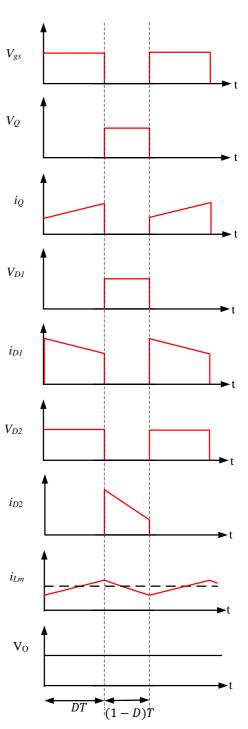

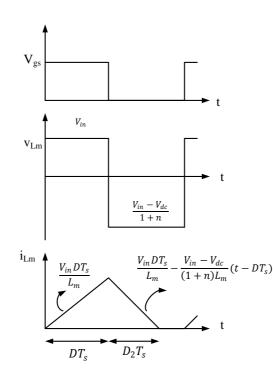

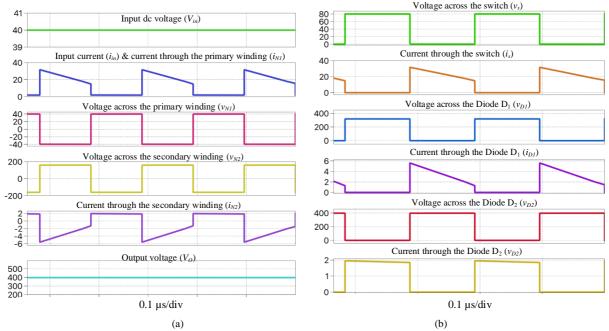

According to the prior art assumptions, each switching cycle is divided into two modes of operation as shown in Fig. 2(a) and Fig. 2(b). The key waveforms in one switching cycle in CCM are shown in Fig. 3. In Mode 1, as shown in Fig. 2(a), the power switch is turned ON, and the voltage across  $L_m$  is equal to the input voltage. Moreover,  $D_1$  is ON and  $D_2$  is OFF during this mode, where  $C_{dc}$  is delivering energy to the load, connected across  $C_{out}$ . Hence, from Fig. 2(a)

$$V_{Lm(mode1)} = V_{in} \tag{1}$$

Then, applying the KVL in secondary winding, the following equation can be obtained as:

$$V_0 = V_{Cdc} + nV_{dc} \qquad \text{Where } n = \frac{n_2}{n_1} \tag{2}$$

Mode 2 starts when the power switch is turned OFF, in which  $D_2$  is ON and providing a current path for the magnetizing inductance current. During this mode,  $D_1$  is OFF and the output capacitor delivers the required energy to the load. Thus, applying KVL again, the voltage across  $L_m$  is given by

$$V_{Lm(mode2)} = \frac{V_{in-V_{dc}}}{1+n} \tag{3}$$

Due to the voltage-second balance of  $L_m$ , the following expression can be obtained:

$$DV_{in} + \frac{(1-D)(V_{in} - V_{Cdc})}{1+n} = 0$$

(4)

Therefore, the voltage across  $C_{dc}$  is obtained as

$$V_{C_{dc}} = \frac{(1+nD)}{1-D} V_{in}$$

(5)

Substituting (5) into (2), the output voltage is given by

Fig. 3. Key waveforms of the proposed converter in continuous conduction mode.

$$V_O = \frac{1+n}{1-D} V_{in} \tag{6}$$

Using (6), the voltage gain of the proposed converter is

$$G = \frac{1+n}{1-D} \tag{7}$$

Hence, it is obvious that the output voltage is a function of the transformer turns ratio (n) or the duty cycle (D). The voltage stress across the power switch is obtained by applying KVL in Fig. 2(b) as follows:

$$V_S = V_{in} - V_{Lm(mode2)} \tag{8}$$

Using (3) and (5), we have

$$V_{S} = V_{in} - \frac{(V_{in} - V_{C1})}{1+n} = \frac{V_{in}}{1-D}$$

(9)

Comparing (6) and (9), it is clear that voltage stress on the power switch is always lower than output voltage for any turns ratio.

The switching loss can be obtained as

$$P_{S} = C_{S} f_{s} V_{S}^{2} = C_{S} f_{s} (\frac{V_{in}}{1-D})^{2}$$

(10)

Where, Cs is MOSFET drain-source intrinsic capacitor,  $f_s$  is the switching frequency and V<sub>s</sub> is the voltage stress across the power switch. From (10), it is obvious that the power loss can be decreased n<sup>2</sup> times compared to the conventional coupled inductor SEPIC converter. Moreover, the low voltage power MOSFET has lower turn-on resistance that can lead to lower conduction losses and consequently gives a better efficiency.

Similarly, the  $R_{DS,on}$  of the device increases with the blocking voltage capability of the device. Hence, lower voltage device as implemented in the circuit has lower  $R_{DS,on}$ , which consequently have lower conduction loss. Hence, with the reduction of the voltage stress both switching and conduction losses are reuced.

Similarly, the voltage stress across  $D_1$  and  $D_2$  can be obtained by

$$V_{D1} = \frac{nV_{in}}{1-D} \tag{11}$$

$$V_{D2} = V_0 = \frac{1+n}{1-D} V_{in} \tag{12}$$

The current stress of the different components can be determined using the charge balance of the capacitors. According to Fig. 2(b), the output capacitor current is equal to the output current in Mode 2. Therefore,

$$I_{cout}(Mode\ 2) = -I_0 \tag{13}$$

Similarly, due to the charge balance in  $C_{out}$ , the following equation can be obtained:

$$I_{Cout}(Mode \ 1) = \frac{(1-D)I_O}{D} \tag{14}$$

The average value of the current in  $D_I$  ( $\langle I_{D1} \rangle$ ) is equal to output current, i.e.

$$\langle I_{D1} \rangle = I_0 \tag{15}$$

Thus, the maximum current in  $D_1$  can be determined by

$$I_{D1} = \frac{I_0}{D} \tag{16}$$

Using Fig. 2, the average values of the transformer primary and secondary current are equal to zero. Therefore, the average current in  $D_2$  ( $<I_{D2}>$ ) is given by

$$\langle I_{D2} \rangle = I_0 \tag{17}$$

The maximum current in  $D_2$  is given by

$$I_{D2} = \frac{I_o}{1 - D}.$$

(18)

Moreover, from Fig. 2(a), the average value of the MOSFET current ( $\langle I_Q \rangle$ ) is given by

$$< l_{Q} >= < l_{Lm} > -n < l_{D1} >$$

(19)

The average value of the magnetizing inductor current is equal to the average input current. Since the average value of the transformer primary current is zero, the following equation can be obtained:

$$< I_0 > = < I_{in} > -n I_o,$$

(20)

which results in

$$< I_Q >= \frac{1+Dn}{1-D} I_o.$$

(21)

Therefore, the maximum current in the MOSFET can be calculated by using

$$I_{S} = \frac{1+Dn}{D(1-D)} I_{o}.$$

(22)

#### **B.** BCM and DCM operations

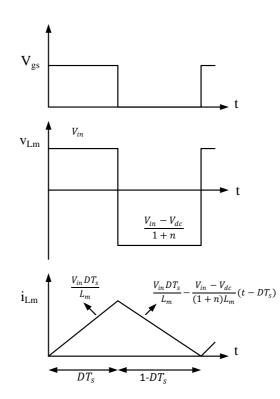

The proposed converter goes to boundary conduction mode (BCM) when the magnetizing inductor current drops to zero exactly in the next switching cycle. The magnetizing inductance current and voltage in this mode are shown in Fig. 4. This phenomenon occurs when the magnetic inductance or switching frequency values are small or the converter works under light load conditions. If the inductor current goes to zero before the next switching cycle, the converter works in discontinuous conduction mode (DCM). In the following context, the condition under which the converter goes to the BCM is derived, and then the voltage gain of the converter under DCM is obtained. From Fig. 4, the current ripple across the magnetic inductance is given by

4

$$\Delta i_{Lm} = \frac{V_{in}DT_s}{L_m}.$$

(23)

Also, the average value of the magnetizing current ( $\langle i_{Lm} \rangle$ ) is

$$\langle i_{Lm} \rangle = \frac{\Delta i_{Lm}}{2} = \frac{V_{in}DT_s}{2L_m}.$$

(24)

The average current value of the transformer primary and secondary winding is equal to zero due to the series capacitor ( $C_{dc}$ ) with secondary winding. Thus, applying KCL results in

$$\langle i_{Lm} \rangle = \langle i_{in} \rangle, \tag{25}$$

Fig. 4. Magnetizing inductance voltage and current in BCM.

where,  $\langle i_{in} \rangle$  is the average value of the input current. If all parasitic effects are neglected the input power is equal to output power, i.e.

$$P_o = P_{in}.$$

(26)

Or in another way

$$v_{in}i_{in} = v_o i_o \tag{27}$$

The voltage gain of the converter in the BCM can be obtained using (6). Therefore, substituting (6) and (25) into (27) can lead to

$$\frac{V_{in}D}{2L_m f_s} = \frac{(1+n)}{1-D} i_{OB},$$

(28)

where  $f_s$  is the switching frequency and  $i_{OB}$  is the output current under BCM.

Therefore, the boundary output current can be obtained from

$$i_{OB} = \frac{D(1-D)^2 V_0}{2L_m f_s (1+n)^2}.$$

(29)

Using the above equation, the normalized boundary output current is given by

$$\frac{\dot{L}_{OB}}{2L_{mfs}} = \frac{D(1-D)^2}{(1+n)^2},$$

(30)

Using (28), the minimum value of the magnetizing inductor that is required in order to operate the converter in CCM can be obtained by

$$L_m \ge \frac{D(1-D)^2 V_0}{2f_s i_{0B}(1+n)^2} \tag{31}$$

The converter goes to DCM if the magnetizing inductance value is lower than (31) for a certain load.

The boundary load resistance and its normalized value can also be obtained as in (32) and (33) respectively, where

$$R_{OB} = \frac{2L_m f(1+n)^2}{D(1-D)^2},$$

(32)

$$\frac{R_{OB}}{2L_m f_s} = \frac{(1+n)^2}{D(1-D)^2}.$$

(33)

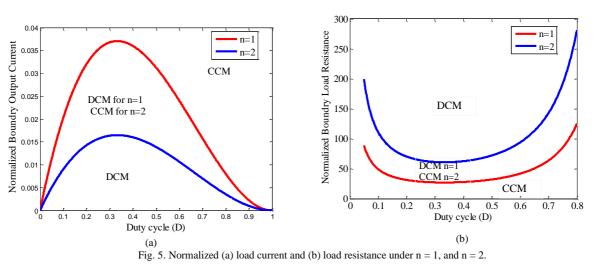

The normalized output current and the normalized output resistance are plotted in Fig. 5(a) and Fig. 5(b) respectively for n=1 and n=2. It is clear that the CCM region can be extended with increasing the coupled inductors turn ratio. The maximum value of the boundary output current can be obtained from the derivative of (29), that occurs under D=1/3 and gives the maximum value of the boundary output current as

$$i_{O(\max)} = \frac{V_0}{54L_m f_s (1+n)^2}.$$

(34)

There are three regions in DCM. Modes 1 and 2 are similar to Fig. 2(a) and Fig. 2(b) respectively, while Mode 3 is shown in Fig. 6.

Fig. 6. Mode 3 in Discontinuous Conduction Mode (DCM).

Fig. 7. Magnetizing inductance voltage and current in DCM.

In this mode, the switch and the two diodes are turned OFF and the magnetizing inductor current fall to zero before the next switching cycle. The magnetizing current under DCM is shown in Fig. 7. Hence, the following equations can be derived by using Fig. 7.

$$i_{PK} = \frac{V_{inDT_s}}{L_m},\tag{35}$$

$$< i_{Lm} > = \frac{i_{PK}(D+D_2)}{2} = \frac{V_{in}D(D+D_2)}{2L_m f_s},$$

(36)

As shown in Fig. 7,  $D_2T_s$  is the time taken by the inductor current  $i_{Lm}$  to fall to zero from its peak value (i.e. at the end of  $V_{gs}$  ON).

As discussed before, the average value of the magnetizing inductor current is equal to input current, i.e.

$$\langle i_{Lm} \rangle = \langle i_{in} \rangle. \tag{37}$$

Also, the output power is equal to the input power if all parasitic effects are neglected i.e.

$$P_{in} = P_0 \Rightarrow \frac{V_{in}^2 D(D+D_2)}{2L_m f_s} = \frac{V_0^2}{R}.$$

(38)

Due to the voltage-second balance of the magnetizing inductance, the following relation can be obtained:

$$DV_{in} + \frac{D_2(V_{in} - V_{CdC})}{1+n} = 0.$$

(39)

Substituting (2) into (39) leads to

$$D_2 = \frac{D(n+1)V_{in}}{V_O - (n+1)V_{in}}.$$

(40)

The relationship between D and the voltage gain of the converter during the DCM can eventually be derived by substituting (40) into (38) as follows:

$$D = \sqrt{2\tau M_{DCM} (M_{DCM} - (n+1))},$$

(41)

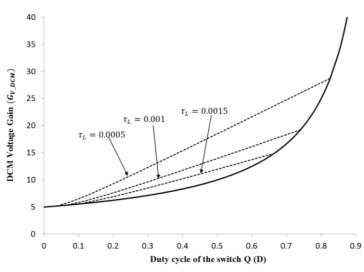

Fig. 8. Voltage gain versus duty ratio at DCM operation under various  $\tau_L$  values and n = 4.

where the normalized input time constant  $\tau_L$  is given by

$$t_L = \frac{L}{RT_S} = \frac{Lf_S}{R},\tag{42}$$

Where  $f_s$  is the switching frequency and R is the equivalent load resistance. Curves illustrating (41) are shown in Fig. 8 for different  $\tau_L$  values during the DCM operation. From (41), it is quite obvious that the voltage gain is load dependent during the DCM. Finally, the DCM is not recommended in general.

## C. Design guidelines

The component values in the proposed converter can be determined considering the following specifications:

- 1) input voltage varies between 30 V and 50 V and its nominal value is 40 V;

- 2) output voltage is fixed to 400 V;

- 3) switching frequency is set to be 100 KHz;

- 4) nominal output power equals 400 W, corresponding to  $I_0=1 A$ ;

- 5) converter works in CCM;

- 6) voltage stress on power switch should be lower than *150 V*, which is the rated value of the selected MOSFET; and

- 7) Voltage ripple across the capacitors should be lower than 1% of their nominal values.

Using (11), the voltage stress across the switch can be determined as

$$V_{\rm S} = \frac{V_0}{1+n} \tag{43}$$

Using (43), in order to restrict the voltage stress across the switch to 80 V, n should be equal to or higher than 4. Therefore, in the experimental prototype n=4 is selected

The minimum and maximum value of the duty cycle is determined using (7)

$$D_{\min} = 1 - \frac{(1+n)V_{in\max}}{V_0} = 1 - \frac{5 \times 50}{400} = 0.375$$

(44)

$$D_{\max} = 1 - \frac{(1+n)V_{in\min}}{V_0} = 1 - \frac{5 \times 30}{400} = 0.625$$

(45)

Also, the nominal value of the duty cycle is determined as D=0.5

Using (31), in order to maintain the converter operates in CCM in half load ( $I_0=0.5 A$ ) and maximum input voltage, the minimum value of the magnetizing inductance can be determined as

$$L_{\rm m}({\rm min}) \ge \frac{0.375 \times (1 - 0.375)^2 \times 400}{2 \times 100 \times 10^3 \times 25 \times 0.5} = 23.43 \,\mu H \tag{46}$$

Finally, a coupled inductor with n=4 and  $L_m = 39 \,\mu H$  is utilized in the experimental prototype.

Moreover, the maximum value of the voltage across  $D_1$ , obtained from (11) is

$$V_{D1} = \frac{nV_{in(max)}}{1-D} = \frac{4 \times 40}{1-0.5} = 320 \text{ V.}$$

(47)

The voltage stress on  $D_2$  is equal to the output voltage that is 400 V.

The output capacitor current is equal to the output current in Mode 2. Therefore, the voltage ripple across this capacitor can be determined as

$$\Delta V_{\text{Cout}} = \frac{(1-D)I_{\text{O}}}{C_{\text{out}}f}$$

(48)

Therefore,

$$C_{out(min)} = \frac{(1 - D_{max})I_0}{f\Delta V_{Cout}} = \frac{(1 - 0.55) \times 1}{100 \times 10^3 \times 4} = 1.125 \,\mu F$$

(49)

As a result, a 1  $\mu$ F ceramic capacitor is selected in the experimental prototype. At nominal input voltage, the output voltage ripple is slightly higher than 1% of the output voltage value. However, the output voltage ripple can be lower with increasing the size of output capacitor.

$C_{dc}$  current is equal to the D<sub>1</sub> current during Mode 1. This capacitor is discharged in Mode 1 and its voltage is decreased. Therefore, the voltage ripple is

$$\Delta V_{\rm Cdc} = \frac{DI_{D1}}{C_{\rm dc}f} \tag{50}$$

Substituting (16) into (50) gives

$$\Delta V_{\text{Cout}} = \frac{I_O}{C_{dc} f} \tag{51}$$

That determines the minimum value of C<sub>dc</sub> as

$$C_{dc}(\min) \ge \frac{I_0}{f \Delta V_{Cdc(\min)}} = \frac{1}{100 \times 10^3 \times 2.4} = 4.17 \,\mu F$$

(52)

A 4.4 µF, 400 V ceramic capacitor is used in the experimental prototype.

Using (16) and (18) the maximum current stress on  $D_1$  and  $D_2$  can be obtained by

$$I_{D1_{max}} = \frac{I_o}{D_{min}} = \frac{1}{0.375} = 2.66 A$$

(53)

$$I_{D2_{max}} = \frac{I_o}{1 - D_{min}} = \frac{1}{1 - 0.6255} = 2.66 A.$$

(54)

As a result, power diode C3D03060 with a DC blocking voltage 600 V and continuous forward current at11 A at

$T_C = 25^{\circ}C$  is selected for D<sub>1</sub> and D<sub>2</sub>.

The maximum current stress on the power switch can be obtained using (21)

$$I_{Q_{max}} = \frac{(1+nD_{max})I_o}{D_{max}(1-D_{max})} = \frac{(1+4\times0.625)\times1}{0.625\times(1-0.6255)} = 14.93 \ A.$$

(55)

Therefore, a power MOSFET IRFB4321PBF with  $V_{DS} = 150 V$  and  $I_D = 85 A$  is selected.

# III. COMPARISON WITH CONVENTIONAL TOPOLOGIES

## A. Comparison with conventional SEPIC converter

In this section, the proposed converter is compared with conventional coupled inductor SEPIC converter. The voltage gain in the proposed converter is higher for any duty cycle by adding only one diode. With higher voltage gain, the switch voltage stress in the proposed converter is lower than the conventional SEPIC converter when n>1. In order to achieve a high voltage gain, usually n is more than one, which helps to choose a low voltage and low  $R_{DS, ON}$  MOSFETs. This can lead to lower conduction and switching loss and thereby the efficiency can be improved. Another feature of the proposed converter is that the current on the primary and secondary winding, power switch, intermediate capacitor ( $C_{dc}$  in compare with  $C_{ac}$ ) is always lower than the conventional SEPIC converter when  $n \ge 1$ . Table I compares the proposed Quasi-SEPIC converter with its conventional counterpart.

| OMPARISON OF THE PROPOSED CONVERTER FEATURES WITH CONVENTIONAL ISOLATED SEPIC (Fig. 1(a))         Proposed quasi-SEPIC (Fig. 1(a))       Proposed quasi-SEPIC (Fig. 1(b))         Voltage gain expression $\frac{V_0}{V_{tril}}$ $\frac{nD}{1-D}$ $\frac{1+n}{1-D}$ Total no. of components       6       7         No. of switch       1       1         No. of diode       1       1         No. of coupled inductor       1       1         Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ Voltage stress on capacitor $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on witch Q $\frac{n}{2}$ $NA$ $\frac{1+n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on capacitor $C_{ac}$ $nV_{in}$ $\frac{1+n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on witch Q $\frac{n}{0}$ $\frac{N}{0.4}$ $\frac{1+nD}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Current stress on witch Q $\frac{C_{ac}}{0.4c}$ $\frac{NA(e1:\frac{-n}{D})}{\frac{1-D}}$ $\frac{NA(e1:\frac{-n}{D})}{\frac{1-D}$                                                                                                                        | OMPARISON OF THE P                                        |                       | TABLE I.<br>NVERTER FEATURES WITH COU | NVENTIONAL ISOLATED SEPIC CONVERTI |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------|---------------------------------------|------------------------------------|

| Voltage gain expression $\frac{ V_0 }{ V_m }$ $\frac{nD}{1-D}$ $\frac{1}{1-D}$ $\frac{1+n}{1-D}$ Total no. of components<br>(including $C_{in}$ and $C_{out}$ )67No. of switch11No. of capacitor3No. of coupled inductor1Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{DI_0}{D(1-D)}$ $\frac{(n+D)I_0}{D(1-D)}$ Current stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{D_1}{D_0}$ $\frac{n}{1-D}V_{in}$ $\frac{D_1}{D_0}$ $\frac{n}{1-D}V_{in}$ Voltage stress on<br>diode $\frac{D_1}{1-D}V_{in}$ $\frac{D_2}{NA}$ $\frac{1+n}{1-D}V_{in}$ $\frac{Voltage stress oncapacitorC_{ac}\frac{V_{in}}{D_2}\frac{1+n}{D_0}V_{in}\frac{Voltage stress oncapacitorC_{ac}\frac{V_{in}}{D_2}\frac{1+nD_0}{1-D}V_{in}\frac{V_{in}}{D_2}\frac{NA}{1+nD}\frac{V_{in}}{D_0}\frac{1+n}{D_0}V_{in}\frac{V_{in}}{NA}\frac{1+n}{1-D}V_{in}\frac{V_{in}}{D_0}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{1+nD}{1-D}V_{in}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}\frac{V_{in}}{NA}\frac{V_{in}}{1-D}$                           |                                                           | COLOSED CO.           |                                       |                                    |

| Voltage gain expression $\overline{v_{in}}$ $\overline{1-D}$ $\overline{1-D}$ Total no. of components67No. of components67No. of switch11No. of diade12No. of capacitor33No. of coupled inductor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ diode $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>diode $C_{ac}$ $nV_{in}$ NA $Voltage stress oncapacitorC_{ac}nV_{in}NA\frac{1+n}{1-D}V_{in}\frac{1+n}{1-D}V_{in}\frac{1+n}{1-D}V_{in}Voltage stress onwindingC_{ac}nV_{in}NA\frac{1+nD}{1-D}V_{in}\frac{1+nD}{1-D}V_{in}\frac{1+nD}{1-D}V_{in}Current stress onwindingC_{ac}NA\frac{1+nD}{1-D}Voltage stress oncapacitorC_{ac}Node 1: \frac{(n+1)I_0}{D}Mode 2: \frac{(n+1)I_0}{n-D}Mode 2: \frac{nI_0}{1-D}Voltage stress onwindingC_{ac}Node 1: \frac{(n+1)I_0}{D}Mode 2: \frac{(n+1)I_0}{D}Mode 2: \frac{(n+1)I_0}{D}Node 2: \frac{I_0}{1-D}Current stress oncapacitorC_{ac}NAMode 1: \frac{I_0}{D}D_1\frac{I_0}{D_2}NA\frac{I_0}{D_0}IodeD_1\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}V_0$                                                                                                                                                                | 1 di di li li ci      |                       | 52110 (11g. 1(u))                     |                                    |

| Total no. of components $1-D$ $1-D$ No. of switch11No. of switch11No. of diode12No. of capacitor33No. of capacitor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switchQ $\frac{nDI_0}{D(1-D)}$ $\frac{(n+D)I_0}{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ $\frac{I+nD}{1-D}V_{in}$ $\frac{1+nD}{1-D}V_{in}$ $\frac{1+nD}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $\frac{V_{in}}{D_2}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $Mode 2: \frac{(n+1)I_0}{D}$<br>$\frac{Node 2: \frac{(n+1)I_0}{n(1-D)}}$ $Mode 1: \frac{I_0}{D}$ $Voltage stress onwindingC_{ac}NA\frac{Na}{1-D}NA\frac{D_1}{1-D}\frac{I_0}{D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}$                                                                                                                          | Voltage gain expression $\left[\frac{V_0}{V_{in}}\right]$ |                       | nD                                    | 1 + n                              |

| Total no. of components67No. of components67No. of switch11No. of switch12No. of capacitor33No. of coupled inductor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ Voltage Stress on diode $D_1$ $\frac{n}{1-D}V_{in}$ $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on capacitor $C_{ac}$ $nV_{in}$ No diode $\frac{l_{ac}}{L_{ac}}$ $nV_{in}$ No diade $\frac{l_{ac}}{L_{ac}}$ $nV_{in}$ No diade $\frac{l_{ac}}{L_{ac}}$ $nV_{in}$ No del : $\frac{(n+1)I_0}{D}$ $Mode 1: \frac{nI_0}{D}$ Voltage stress on winding $C_{ac}$ $nV_{in}$ No del : $\frac{(n+1)I_0}{D}$ $Mode 1: \frac{nI_0}{D}$ $Mode 2: \frac{(n+1)I_0}{1-D}$ $Mode 2: \frac{nI_0}{1-D}$ $Voltage stress on windingC_{ac}Mode 1: \frac{(n+1)I_0}{D}Mode 2: \frac{(n+1)I_0}{1-D}Mode 2: \frac{nI_0}{1-D}Mode 2: \frac{(n+1)I_0}{D}Mode 2: \frac{nI_0}{1-D}Mode 2: \frac{(n+1)I_0}{D}Mode 2: \frac{I_0}{1-D}Mode 2: \frac{(n+1)I_0}{D}Mode 2: \frac{I_0}{D}Mode 2: \frac{(n+1)I_0}{D}NAMode 2: \frac{(n-1)I_0}{D}NAMode 2: \frac{(n-1)}{1-D}I_0Mode 2: \frac{(n-1)}{1-D}I_0I_0 =I_0I_0 =I_0I_0 =I_0I_0 =I_0$                                                                                                                                                              |                                                           |                       | $\overline{1-D}$                      | $\overline{1-D}$                   |

| No. of switch11No. of diode12No. of capacitor33No. of coupled inductor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switch Q $\frac{nDI_o}{D(1-D)}$ $\frac{(n+D)I_o}{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ Voltage stress on<br>winding $C_{ac}$ $nV_{in}$ $NA$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ Current stress on<br>winding $C_{ac}$ $nV_{in}$ $NA$ $Voltage stress oncapacitorC_{ac}NA\frac{1+nD}{1-D}V_{in}Current stress oncapacitorC_{ac}NA\frac{1+nD}{b_0}Mode 1: \frac{-(n+1)I_0}{b}Mode 2: \frac{(n+1)I_0}{n}Mode 1: \frac{I_0}{b}Mode 2: \frac{(n+1)I_0}{n}Mode 2: \frac{(n+1)I_0}{n}Mode 2: \frac{I_0}{1-D}Current stress ondiodeC_{dc}NAMode 1: \frac{I_0}{b}Current stress ondiodeD_1\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}NA\frac{I_0}{1-D}\frac{I_0}{D}$                                                                                                                                                                                                                                                                                          | Total no. of components                                   |                       | 6                                     | 7                                  |

| No. of diode12No. of capacitor33No. of coupled inductor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switchQ $\frac{nDI_0}{D(1-D)}$ $\frac{(n+D)I_0}{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{1-n}{1-D}V_{in}$ Voltage stress on<br>capacitor $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $NA$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ Current stress on<br>winding $C_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ Current stress on<br>winding $C_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ Current stress on<br>diode $C_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ Current stress on<br>capacitor $C_{ac}$ $Mode 1: \frac{(n+1)I_0}{D}$<br>$Mode 2: \frac{(n+1)I_0}{n(1-D)}$ $Mode 1: \frac{I_0}{D}$ Current stress on<br>diode $C_{ac}$ $Mode 1: \frac{(n+1)I_0}{D}$<br>$Mode 2: \frac{(n+1)I_0}{1-D}$ $NA$ Current stress on<br>diode $D_1$ $\frac{I_0}{1-D}$ $NA$ $D_2$ $NA$ $\frac{I_0}{1-D}$                                                                                                                                                                                                                                                                            | (including $C_{in}$ and $C_{oi}$                          | <sub>ut</sub> )       |                                       |                                    |

| No. of capacitor33No. of coupled inductor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switchQ $\frac{nDI_o}{D(1-D)}$ $\frac{(n+D)I_o}{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ Voltage Stress on<br>capacitor $D_2$ $NA$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ Voltage stress on<br>winding $C_{ac}$ $nV_{in}$ $NA$ $V_{in}$ $Mode 1: \frac{-n(n+1)I_o}{D}$ $Mode 1: \frac{nI_o}{D}$ $Mode 2: \frac{(n+1)I_o}{n(1-D)}$ $Mode 1: \frac{nI_o}{D}$ $Mode 2: \frac{nI_o}{1-D}$ $Voltage stress onwindingi_{N2}Mode 1: \frac{-(n+1)I_o}{D}Mode 2: \frac{nI_o}{1-D}Mode 2: \frac{(n+1)I_o}{n(1-D)}Mode 2: \frac{(n+1)I_o}{n(1-D)}Mode 2: \frac{I_o}{1-D}Mode 2: \frac{(n+1)I_o}{n(1-D)}Mode 2: \frac{I_o}{1-D}NAMode 2: \frac{(n+1)I_o}{n(1-D)}Mode 2: \frac{I_o}{1-D}Mode 2: \frac{(n+1)I_o}{n(1-D)}Mode 2: \frac{I_o}{1-D}Mode 2: \frac{(n+1)I_o}{n(1-D)}Mode 1: \frac{I_o}{D}Mode 2: \frac{(n+1)I_o}{1-D}Mode 2: \frac{I_o}{1-D}Mode 2: \frac{(n+1)I_o}{1-D}NAMode 2: \frac{(n+1)I_o}{1-D}Mode 2: \frac{I_o}{1-D}Mode 2: \frac{(n+1)I_o}{1-D}I_oMode 2: \frac{(n-1)I_o}{1-D}I_oMode 2: \frac{(n-1)I_o}{1-D}I_oMode 2: \frac{(n-1)I_o}{1-D}I_oI_oI_oI_oI_oI_oI_oI_$                                         | No. of switch                                             |                       |                                       | =                                  |

| No. of coupled inductor11Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switch Q $\frac{nDI_o}{D(1-D)}$ $\frac{(n+D)I_o}{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ Voltage Stress on<br>capacitor $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NAVoltage stress on<br>winding $C_{ac}$ $nV_{in}$ NA $Voltage stress oncapacitorC_{ac}nV_{in}NAVoltage stress oncapacitorC_{ac}nV_{in}NAVoltage stress onwindingC_{ac}nV_{in}NAVoltage stress oncapacitorC_{ac}nV_{in}NACurrent stress ondiodeC_{ac}Node 1: \frac{-n(n+1)I_o}{D}Mode 2: \frac{nI_o}{1-D}Voltage stress onwindingC_{ac}Mode 1: \frac{-(n+1)I_o}{D}Mode 2: \frac{nI_o}{1-D}NA\frac{1-nD}{D}Mode 2: \frac{(n+1)I_o}{n(1-D)}Mode 2: \frac{I_o}{1-D}Voltage stress ondiodeC_{ac}NAMode 2: \frac{I_o}{1-D}NA\frac{I_o}{D}NA\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}NA\frac{I_o}{1-D}\frac{I_o}{D}$                                                                                                                                                                                            |                                                           |                       |                                       |                                    |

| Voltage stress on switch Q $\frac{n}{1-D}V_{in}$ $\frac{V_{in}}{1-D}$ Current stress on switch Q $\frac{nDI_0}{D(1-D)}$ $\frac{(n+D)I_0}{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NA $C_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $Voltage stress oncapacitorC_{ac}nV_{in}NAVoltage stress oncapacitorC_{ac}nV_{in}NAVoltage stress oncapacitorC_{ac}NA\frac{1+nD}{1-D}V_{in}Voltage stress oncapacitorC_{ac}NA\frac{1+nD}{1-D}V_{in}Voltage stress oncapacitorC_{ac}NA\frac{1-D}{1-D}V_{in}Voltage stress oncapacitorC_{ac}NA\frac{1+nD}{1-D}V_{in}Voltage stress oncapacitorC_{ac}Node 1: \frac{-n(n+1)I_0}{D}Node 2: \frac{nI_0}{n(1-D)}Voltage stress oncapacitorC_{ac}Node 1: \frac{-(n+1)I_0}{D}Node 2: \frac{-I_0}{1-D}NAMode 1: \frac{-(n+1)I_0}{D}NANANAMode 2: \frac{I_0}{1-D}NAMode 1: \frac{I_0}{D}1-DNAMode 2: \frac{I_0}{1-D}NAMode 2: \frac{I_0}{1-D}NAMode 2: \frac{I_0}{1-D}NAMode 2: \frac{I_0}{1-D}NA\frac{I_0}{1-D}NA\frac{I_0}{1-D}$                                                                                                                                                                                                                                                        |                                                           |                       | 3                                     |                                    |

| $ 1 - D^{+in}$ $1 - D$ Current stress on switchQ $nDI_o$<br>$\overline{D(1-D)}$ $(n+D)I_o$<br>$\overline{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NACurrent stress on<br>winding $C_{ac}$ $nV_{in}$ Mode 1: $\frac{nl_o}{D}$ $i_{N1}$ Mode 1: $\frac{-n(n+1)I_o}{D}$ Mode 2: $\frac{nl_o}{1-D}$ Mode 2: $\frac{(n+1)I_o}{n(1-D)}$ Mode 1: $\frac{nl_o}{D}$ Mode 2: $\frac{(n+1)I_o}{n(1-D)}$ Mode 2: $\frac{nl_o}{1-D}$ Current stress on<br>capacitor $C_{ac}$ Mode 1: $\frac{-(n+1)I_o}{D}$ Mode 2: $\frac{l_o}{1-D}$ Current stress on<br>capacitor $C_{ac}$ Mode 1: $\frac{-(n+1)I_o}{D}$ Mode 2: $\frac{l_o}{1-D}$ Current stress on<br>diode $D_1$ $\frac{I_o}{1-D}$ NA $\frac{I_o}{D_0}$ NA $\frac{I_o}{1-D}$ $\frac{I_o}{D}$ NAD_1 $\frac{I_o}{1-D}$ $\frac{I_o}{D}$ NA $\frac{I_o}{1-D}$ $\frac{I_o}{D}$                                                                                                                                                                                                                                                                                                                                                                                          |                                                           |                       | -                                     | -                                  |

| $\overline{D(1-D)}$ $\overline{D(1-D)}$ $\overline{D(1-D)}$ Voltage Stress on<br>diode $D_1$ $\frac{n}{1-D}V_{in}$ $\frac{n}{1-D}V_{in}$ $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NA $C_{dc}$ NA $\frac{1+nD}{1-D}V_{in}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 1: $\frac{nl_0}{D}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 2: $\frac{nl_0}{1-D}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 2: $\frac{nl_0}{1-D}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 2: $\frac{nl_0}{1-D}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 1: $\frac{l_0}{D}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 1: $\frac{l_0}{D}$ $V_{in}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ $V_{in}$ Mode 1: $\frac{-n(n+1)l_0}{D}$ Mode 2: $\frac{nl_0}{1-D}$ $V_{in}$ <td colspan="2">Voltage stress on switch Q</td> <td><math>\frac{1-D}{1-D}V_{in}</math></td> <td>1 - D</td> | Voltage stress on switch Q                                |                       | $\frac{1-D}{1-D}V_{in}$               | 1 - D                              |

| Under $D_2$ NA $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NA $C_{dc}$ NA $\frac{1+n}{1-D}V_{in}$ $C_{dc}$ NA $\frac{1+nD}{1-D}V_{in}$ $C_{dc}$ NA $\frac{1+nD}{1-D}V_{in}$ $Voltage stress onwindingi_{N1}Mode 1: \frac{-n(n+1)I_O}{1-D}Mode 1: \frac{nI_O}{D}Voltage stress onwindingi_{N2}Mode 1: \frac{-(n+1)I_O}{1-D}Mode 2: \frac{nI_O}{1-D}Voltage stress oncapacitorC_{ac}Mode 1: \frac{-(n+1)I_O}{n}Mode 2: \frac{I_O}{n-D}Current stress oncapacitorC_{dc}NAMode 1: \frac{I_O}{D}Current stress ondiodeD_1\frac{I_O}{1-D}NAD_2NA\frac{I_O}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Current stress on switchQ                                 |                       |                                       | $\frac{(n+D)I_0}{D(1-D)}$          |

| Under $D_2$ $NA$ $\frac{1+n}{1-D}V_{in}$ Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ $NA$ $C_{dc}$ $NA$ $\frac{1+n}{1-D}V_{in}$ $C_{dc}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $C_{dc}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $Voltage stress onwindingMode 1: \frac{-n(n+1)I_0}{D}Mode 1: \frac{nI_0}{D}Voltage stress onwindingNA\frac{1-nD}{1-D}V_{in}Current stress oncapacitorMode 1: \frac{-(n+1)I_0}{D}Mode 2: \frac{l_0}{1-D}Current stress oncapacitorC_{ac}Mode 1: \frac{-(n+1)I_0}{n(1-D)}Mode 2: \frac{l_0}{1-D}Current stress ondiodeD_1\frac{I_0}{1-D}NAMode 2: \frac{l_0}{1-D}D_2NA\frac{I_0}{1-D}D_2NA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Voltago Strass on                                         | D                     |                                       | $\frac{D(1-D)}{n}$                 |

| Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NA $C_{dc}$ NA $\frac{1+nD}{1-D}V_{in}$ $I_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $I_{ac}$ $Mode 1: \frac{-n(n+1)I_0}{D}$ Mode 1: $\frac{nI_0}{D}$ $Mode 2: \frac{(n+1)I_0}{1-D}$ $Mode 2: \frac{nI_0}{1-D}$ $Na$ $Mode 2: \frac{(n+1)I_0}{n(1-D)}$ $Mode 2: \frac{nI_0}{1-D}$ $I_{ac}$ $Mode 1: \frac{-(n+1)I_0}{n(1-D)}$ $Mode 2: \frac{I_0}{1-D}$ $I_{ac}$ $Mode 1: \frac{-(n+1)I_0}{n(1-D)}$ $Mode 2: \frac{I_0}{1-D}$ $I_{ac}$ $Mode 1: \frac{-(n+1)I_0}{n(1-D)}$ $Mode 2: \frac{I_0}{1-D}$ $I_{ac}$ $Mode 1: \frac{-(n+1)I_0}{1-D}$ $NA$ $I_{ac}$ $NA$ $Mode 2: \frac{I_0}{1-D}$ $I_{ac}$ $I_{ac}$ $NA$ $I_{ac}$ $NA$ $I_{ac}$ $I_{ac}$ $NA$ $I_{ac}$ $I_{ac}$ $NA$ $I_{ac}$ <td></td> <td>-</td> <td><math>\frac{1}{1-D}V_{in}</math></td> <td></td>                                                                                                            |                                                           | -                     | $\frac{1}{1-D}V_{in}$                 |                                    |

| Voltage stress on<br>capacitor $C_{ac}$ $nV_{in}$ NA $C_{dc}$ NA $\frac{1+nD}{1-D}V_{in}$ $I_{ac}$ $NA$ $\frac{1+nD}{1-D}V_{in}$ $I_{ac}$ $Node 1: \frac{-n(n+1)I_0}{D}$ Mode 1: $\frac{nI_0}{D}$ $Node 2: \frac{(n+1)I_0}{1-D}$ Mode 2: $\frac{nI_0}{1-D}$ $Na$ $Nade 2: \frac{(n+1)I_0}{n(1-D)}$ Mode 2: $\frac{nI_0}{1-D}$ $I_{ac}$ $Node 1: \frac{-(n+1)I_0}{n(1-D)}$ Mode 2: $\frac{I_0}{1-D}$ $Na$ $Nade 2: \frac{(n+1)I_0}{n(1-D)}$ Mode 2: $\frac{I_0}{1-D}$ $Na$ $C_{ac}$ $Mode 1: \frac{-(n+1)I_0}{n(1-D)}$ NA $Na$ $Nade 2: \frac{(n+1)I_0}{n(1-D)}$ NA $Na$ $Nade 2: \frac{I_0}{1-D}$ $Na$ $Na$ $Na$ $Nade 2: \frac{I_0}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           | <i>D</i> <sub>2</sub> | NA                                    | $\frac{1+n}{1-D}V_{in}$            |

| Current stress on<br>winding $i_{N1}$ Mode 1: $\frac{-n(n+1)l_0}{p}$<br>Mode 2: $\frac{(n+1)l_0}{1-D}$ Mode 1: $\frac{nl_0}{D}$<br>Mode 2: $\frac{nl_0}{1-D}$ $i_{N2}$ Mode 1: $\frac{-(n+1)l_0}{p}$<br>Mode 2: $\frac{(n+1)l_0}{n(1-D)}$ Mode 1: $\frac{l_0}{p}$<br>Mode 2: $\frac{l_0}{1-D}$ $Current stress oncapacitorC_{dc}NACurrent stress ondiodeD_1\frac{l_0}{1-D}D_2NA\frac{l_0}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Voltage stress on                                         | $C_{ac}$              | nV <sub>in</sub>                      |                                    |

| Current stress on<br>winding $i_{N1}$ Mode 1: $\frac{-n(n+1)l_0}{p}$ Mode 1: $\frac{nl_0}{p}$ $i_{N2}$ Mode 2: $\frac{(n+1)l_0}{1-D}$ Mode 2: $\frac{nl_0}{1-D}$ $i_{N2}$ Mode 1: $\frac{-(n+1)l_0}{p}$ Mode 1: $\frac{l_0}{p}$ $Mode 2: \frac{(n+1)l_0}{n(1-D)}$ Mode 2: $\frac{l_0}{1-D}$ $Current stress oncapacitorC_{dc}NACurrent stress ondiodeD_1\frac{l_0}{1-D}D_2NA\frac{l_0}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | capacitor                                                 |                       | NA                                    | $\frac{1+nD}{1-D}V_{in}$           |

| Current stress on<br>windingMode 2: $\frac{(n+1)l_O}{1-D}$ Mode 2: $\frac{nl_O}{1-D}$ $I_{N2}$ Mode 1: $\frac{(n+1)l_O}{D}$ Mode 1: $\frac{l_O}{D}$ Mode 2: $\frac{(n+1)l_O}{n(1-D)}$ Mode 1: $\frac{l_O}{D}$ Mode 2: $\frac{l_O}{1-D}$ Mode 2: $\frac{(n+1)l_O}{n(1-D)}$ Mode 2: $\frac{(n+1)l_O}{n(1-D)}$ Mode 2: $\frac{l_O}{1-D}$ Current stress on<br>capacitor $C_{dc}$ NAMode 1: $\frac{l_O}{D}$ Current stress on<br>diode $D_1$ $\frac{l_O}{1-D}$ $\frac{l_O}{D}$ D1 $\frac{l_O}{1-D}$ $\frac{l_O}{D}$ $\frac{l_O}{D}$ NA $\frac{l_O}{1-D}$ $\frac{l_O}{D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           | i <sub>N1</sub>       | Mode 1: $\frac{-n(n+1)I_0}{n}$        |                                    |

| Current stress on<br>diode $C_{ac}$ Mode 2: $\frac{(n+1)l_o}{n(1-D)}$ Mode 2: $\frac{l_o}{1-D}$ Current stress on<br>capacitor $C_{ac}$ Mode 1: $\frac{(n+1)l_o}{D_b}$<br>Mode 2: $\frac{(n+1)l_o}{1-D}$ NACurrent stress on<br>diode $D_1$ $\frac{l_o}{1-D}$ $\frac{l_o}{D_c}$ D_2NA $\frac{l_o}{1-D}$ $\frac{l_o}{D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Current stress on                                         |                       |                                       |                                    |

| Current stress on<br>capacitor $C_{ac}$ Mode $2: \frac{(n+1)l_0}{n(1-D)}$<br>Mode $1: \frac{-(n+1)l_0}{b}$<br>Mode $2: \frac{(n+1)l_0}{1-D}$ NACurrent stress on<br>diode $C_{dc}$ NAMode $1: \frac{l_0}{D}$<br>$\frac{1-D}$ Current stress on<br>diode $D_1$ $\frac{l_0}{1-D}$ $\frac{l_0}{D}$<br>$\frac{D_2}$ NA $\frac{l_0}{1-D}$ $\frac{l_0}{D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | winding                                                   | i <sub>N2</sub>       | Mode 1: $\frac{-(n+1)I_0}{D}$         | Mode 1: $\frac{I_O}{D}$            |

| Current stress on<br>capacitor $C_{dc}$ Mode 2: $\frac{(n+1)I_0}{1-D}$ NACurrent stress on<br>diode $D_1$ $\frac{I_0}{1-D}$ $\frac{I_0}{D}$ D_2NA $\frac{I_0}{1-D}$ $\frac{I_0}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                           |                       | Mode 2: $\frac{(n+1)I_0}{n(1-D)}$     | Mode 2: $\frac{I_0}{1-D}$          |

| Current stress on<br>capacitor $C_{dc}$ Mode 1: $\frac{l_0}{p}$<br>Mode 2: $\frac{l_0}{1-p}$ Current stress on<br>diode $D_1$ $\frac{l_0}{1-D}$ $D_2$ $D_2$ $D_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                           | C <sub>ac</sub>       | Mode 1: $\frac{-(n+1)l_0}{D}$         |                                    |

| CapacitorNAMode 2: $\frac{\overline{I_o}}{1-D}$ Current stress on<br>diode $D_1$ $\frac{I_o}{1-D}$ $\frac{I_o}{D}$ $D_2$ NA $\frac{I_o}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                       | Mode 2: $\frac{(n+1)I_0}{1-D}$        |                                    |

| Image: Definition of the second systemMode 2: $\frac{I_0}{1-D}$ Current stress on<br>diode $D_1$ $\frac{I_0}{1-D}$ $D_2$ $D_2$ $\frac{I_0}{1-D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | C <sub>dc</sub>       | NΔ                                    | Mode 1: $\frac{I_0}{D}$            |

| NA 1-D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | *                                                         |                       | · · · · · · · · · · · · · · · · · · · | Mode 2: $\frac{l_0}{1-D}$          |

| NA 1-D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           | $D_1$                 |                                       | $\frac{I_o}{D}$                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           | <i>D</i> <sub>2</sub> |                                       | $\frac{I_0}{1-D}$                  |

| Note: NA is not applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           |                       | Note: NA is not applic                |                                    |

TABLE I.

## B. Comparison with other converter with similar voltage gain

Higher boost converter topologies are also available in the literature using multi-stage and/or voltage multiplier cells or using multiple winding coupled inductors. However, for a fair comparison, only topologies with one two-winding coupled inductor type converter with one active switching device and similar voltage stress are considered for comparison. Hence quadratic boost type and topologies with two or more than two switches are excluded from the comparison along with three winding coupled inductor topologies. Table II compares the proposed converter with other two winding coupled inductor converters.

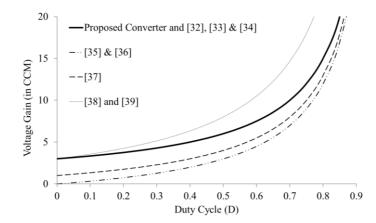

Topologies presented in [32]-[34] produce the same voltage gain as of the proposed topology; however the number of capacitors and diodes are higher than the proposed topology. With two magnetic elements in [35]-[37], these converters require more space whilst their voltage gains are significantly lower. Similarly, the voltage gain for the topology presented in [38] and [39] are higher than the proposed converter; however, the number of components is higher than the proposed topology. These two topologies are considered to be compared fair with the extended circuit of the proposed topology and hence will be discussed in Section IV. Fig. 9 compares the voltage gain of the proposed converters in [32]-[39].

TABLE II

COMPARISON OF THE PROPOSED CONVERTER WITH DIFFERENT TWO WINDING COUPLED INDUCTOR BASED SINGLE SWITCH HIGH VOLTAGE DC-DC CONVERTERS

| CONVERTERS.                           |                              |                   |                      |   |   |    |     |

|---------------------------------------|------------------------------|-------------------|----------------------|---|---|----|-----|

| Ref.                                  | Voltage Gain                 | Voltage Stress on | No. of components    |   |   |    |     |

|                                       | $(G_v = \frac{V_0}{V_{dc}})$ | Switch            | Coupled-<br>inductor | L | D | C* | S/W |

| Proposed<br>Converter                 | $\frac{1+n}{1-D}$            | $V_{dc}/(1-D)$    | 1                    | 0 | 2 | 3  | 1   |

| Converter in [32]                     | $\frac{1+n}{1-D}$            | $V_{dc}/(1-D)$    | 1                    | 1 | 2 | 4  | 1   |

| Converter in [33]                     | $\frac{1+n}{1-D}$            | $V_{dc}/(1-D)$    | 1                    | 1 | 4 | 5  | 1   |

| Converter in [34]                     | $\frac{1+n}{1-D}$            | $V_{dc}/(1-D)$    | 1                    | 0 | 3 | 4  | 1   |

| Converter in [35]<br>and [36]         | $\frac{D(1+n)}{1-D}$         | $V_{dc}/(1-D)$    | 1                    | 1 | 2 | 2  | 1   |

| Converter in [37]                     | $\frac{1 + nD}{1 - D}$       | $V_{dc}/(1-D)$    | 1                    | 1 | 2 | 3  | 1   |

| Converter in [38],<br>And[39]         | $\frac{1+n+nD}{1-D}$         | $V_{dc}/(1-D)$    | 1                    | 0 | 4 | 5  | 1   |

| *Including input and output capacitor |                              |                   |                      |   |   |    |     |

Fig. 9. Comparison of voltage gain of the proposed converter with different two-winding inductor based high boost single switch-switch dc-dc converter in CCM (n = 2).

# IV. DERIVATIVE CONVERTER WITH HIGHER VOLTAGE GAIN

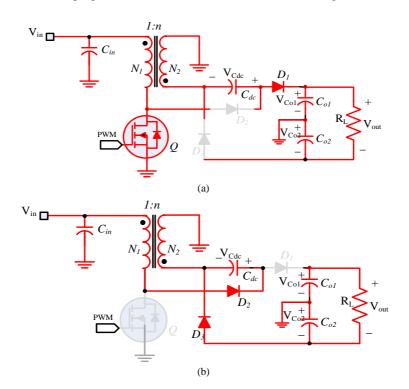

The voltage gain of the proposed converter can be raised further by adding one diode and one capacitor to its structure as shown in Fig. 10. The output capacitor  $C_0$  is split into two capacitors ( $C_{01} \& C_{02}$ ) and  $D_3$  is inserted between the negative terminal of the load and the secondary winding of the transformer. In CCM as shown in Fig. 11, there are two modes in one switching cycle. When the power switch is turned ON, the diode  $D_1$  becomes forward biased while diodes  $D_2$  and  $D_3$  become reverse biased. When the power switch is turned OFF, the diode  $D_1$  is turned OFF while  $D_2$  and  $D_3$ are ON. Similar analysis can be made for this extended gain converter as well.

Fig. 10. Derivative circuit of quasi-SEPIC for higher voltage gain.

Appling the voltage-second balance principle on the magnetizing inductance leads to

$$DV_{in} + (1-D)\frac{V_{in} - V_{cdc}}{1+n} = 0$$

(56)

That results in

$$V_{Cdc} = \frac{1+nD}{1-D} \tag{57}$$

Using KVL in Mode 1

$$V_{Co1} = V_{Cdc} + nV_{in} = \frac{1+n}{1-D}V_{in}$$

(58)

Also, the voltage across  $V_{Co2}$  can be obtained using KVL in Mode 2

$$V_{Co2} = \frac{Dn}{1-D} \tag{59}$$

Therefore, the output voltage can be obtained using (58) - (59)

$$V_o = V_{Co1} + V_{Co2} = \frac{1 + n + nD}{1 - D} V_{in}$$

(60)

The voltage stress across the power switch and diodes can be expressed as given in the following equations

$$V_{D1} = \frac{nV_{in}}{1-D} \tag{61}$$

$$V_{D2} = \frac{(1+n)V_{in}}{1-D}$$

(62)

$$V_{D3} = \frac{nV_{in}}{1-D} \tag{63}$$

$$V_{\mathcal{S}} = \frac{V_{in}}{1-D}.$$

(64)

Comparing (61) - (64) with the output voltage, it is clear that the voltage stress on all semiconductor devices is lower than the output voltage. Particularly, although the voltage gain can be raised compared with the elementary converter proposed in Fig. 1, the voltage stress on the switch remains unchanged. Therefore, the power switch with low ON resistance ( $R_{DS,ON}$ ) can be utilized that can lead to lower conduction loss and higher efficiency.

From the voltage gain view-point, the derivative of the proposed converter has equal voltage gain with converters that have been presented in [38]-[39]. However, there are fewer components in the proposed converter in Fig.10. Refer to Table II, there are five capacitors and four diodes in the presented converters in [38]-[39], while there are four capacitors and three diodes in the proposed extension of the converter shown in Fig. 11.

Fig. 11. Equivalent circuits during one switching cycle (a) Mode 1 ( $Q_{ON}$ ), and (b) Mode 2 ( $Q_{OFF}$ ).

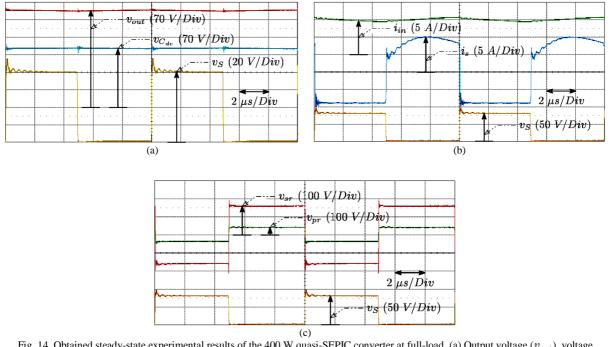

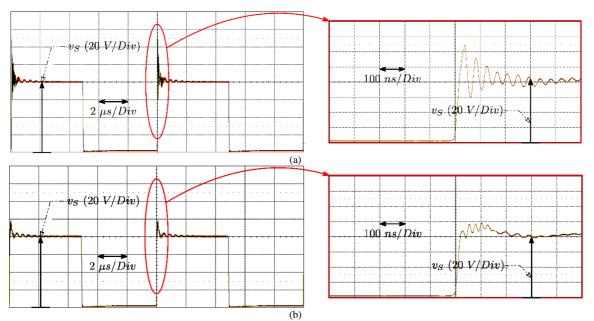

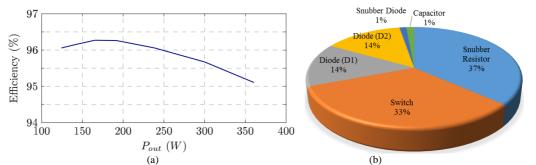

#### V. SIMULATION AND EXPERIMENTAL RESULTS