# An 8-b 400-MS/s 2-b-Per-Cycle SAR ADC With Resistive DAC

Hegong Wei, Member, IEEE, Chi-Hang Chan, Student Member, IEEE, U-Fat Chio, Sai-Weng Sin, Member, IEEE, Seng-Pan U, Senior Member, IEEE, Rui Paulo Martins, Fellow, IEEE, and Franco Maloberti, Fellow, IEEE

Abstract—An 8-b 400-MS/s 2-b-per-cycle (2 b/C) successive approximation register (SAR) analog-to-digital converter (ADC) is fabricated in 65-nm CMOS. With the implementation of a low-power and small-area resistive DAC and associated highly integrated circuit implementation, the proposed SAR ADC achieves rapid conversion rate, low power, and compact area, leading to SNDR of 44.5 dB and SFDR of 54.0 dB, at 400 MS/s with 1.9-MHz input. The measured FOM is 73 fJ/conversion-step at 400 MS/s from 1.2-V supply and 42 fJ/conversion-step at 250 MS/s from a 1-V supply. The active area with the digital calibration is 0.028 mm².

Index Terms—Analog-to-digital converter (ADC), resistive DAC, successive approximation register (SAR), 2-b-per-cycle (2 b/C).

#### I. INTRODUCTION

UCCESSIVE approximation register (SAR) analog-todigital converters (ADCs), which perform the conversion with only one comparator, achieve lower power with higher efficiency when compared with other types of ADCs [1]–[4]. Based on its highly digitized architecture, state-of-the-art SAR ADCs consume less and less power benefiting from CMOS technology down-scaling and provide very efficient solutions for a wide range of specifications. Typically, the SAR ADC is appropriate for low-bandwidth applications because it requires N+1 or more clock cycles to obtain N-bit resolution. Achieving a moderate resolution SAR ADC for very high-speed applications, namely, over 150 MS/s, implies a tough design of the dynamic comparator. Time-interleaved implementations enhance the speed, but imperfections such as timing skew and channel mismatch limit the resolution [4]. Obviously, the power effectiveness remains the same because an increased speed entails the multiplication of hardware and power.

An effective way used to augment speed is employing more than one bit per SAR cycle [5]. Multiple comparators make

Manuscript received December 24, 2011; revised April 23, 2012; accepted June 27, 2012. Date of publication September 24, 2012; date of current version October 26, 2012. This paper was approved by Associate Editor Anthony Chan Carusone. This work was supported in part by the University of Macau and the Macao Science & Technology Development Fund (FDCT).

H-G. Wei, C.-H. Chan, U-F. Chio, S.-W. Sin, and S.-P. U are with The State Key Lab of Analog and Mixed Signal VLSI, Faculty of Science and Technology, University of Macau, Macao, China (e-mail: weihegong@ieee.org).

R. P. Martins is with The State Key Lab of Analog and Mixed Signal VLSI, Faculty of Science and Technology, University of Macau, Macao, China, on leave from Instituto Superior Técnico/TU, Lisbon, Portugal.

F. Maloberti is with The State Key Lab of Analog and Mixed Signal VLSI, Faculty of Science and Technology, University of Macau, Macao, China, and also with the University of Pavia, 27100 Pavia, Italy.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2012.2214181

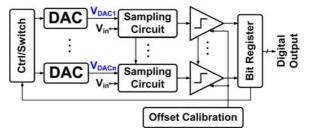

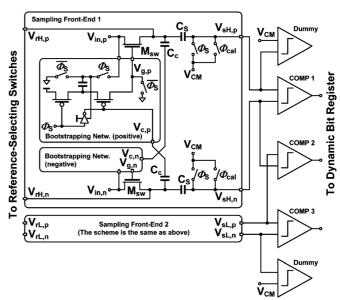

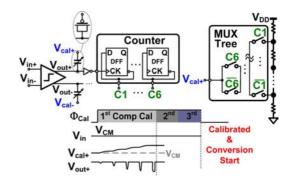

Fig. 1. Architecture of Mb/C SAR ADC.

a conventional SAR ADC topology a multibit/cycle (Mb/C) SAR. The number of conversion periods diminishes by a factor equal to the number of bits per SAR cycle. However, more than two-bit/cycle (2 b/C) is not recommended because multiple reference voltages required for the comparator's decision, which must be generated with a proper accuracy, increase the area and the power. In addition, the comparator offsets induce linearity errors, which degrade the ADC accuracy.

This design is a power-efficient ADC solution with up to 400-MS/s conversion rate based on a (2 b/C) SAR topology that uses a resistive-based 2-b DAC and several power/area reduction techniques [6], like interpolation [7] in the sampling network, which reduces 33% of the hardware of the sampling circuit, DAC switches, and digital decoder. Moreover, cascaded inverters in the decoder instead of the conventional AND/NAND gates saves about half the number of transistors, leading to low-power performance and faster operation. Furthermore, a cross-coupled bootstrapping network alleviates the signal-dependent clock feed-through.

In the organization of this paper, Section II presents the architecture analysis of the resistive DAC-based SAR ADC in order to obtain optimum performance. Section III introduces the implementation of the proposed ADC with different circuit techniques that comprise interpolated sampling circuits, cross-coupled bootstrapping network, resistive DAC, cascaded-inverter based decoder, and offset calibration. Section IV describes the layout considerations achieving a very compact design that allows significant power reduction. In Section V, the experimental results obtained from a 65-nm CMOS chip implementation clearly demonstrate the ADC performance. The conclusions are drawn in Section VI.

## II. ADC ARCHITECTURE AND ANALYSIS

Fig. 1 shows the conceptual block diagram of an Mb/C SAR ADC where sampled input signals are successively compared to voltages ( $V_{\rm DAC1}$  to  $V_{\rm DACn}$ ) generated by multiple DACs. The requirement of minimizing the mismatch of comparators' offset voltage is satisfied by digital offset calibration network.

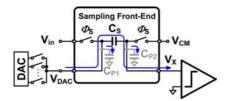

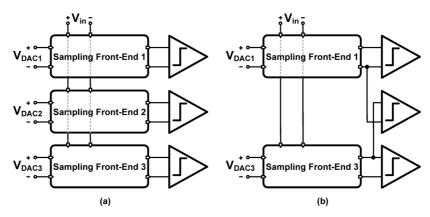

Fig. 2. Passive sampling front-end circuit.

Following the comparator array, a bit register and a switching network performs the SAR algorithm to determine the digital input of the DACs. The Mb/C structure effectively increases the speed of the ADC, allowing a SAR ADC structure to operate in high-bandwidth applications [8], [9].

There are two possible solutions for the DAC: capacitive or resistive schemes. The capacitive DAC uses a circuit like the one proposed in [5], where a suitable capacitor array, which consumes dynamic power, generates the reference voltages. However, even with two bits, the voltages needed by a differential implementation lead to a six-capacitances scheme, which means large area and capacitive load.

Early implementations [10] used resistive DACs, but the static power imposed by the required fast settling makes them unsuitable for low power (or occupying large area), especially for N bits resolution that requires  $2^N$  switches and control logic associated with heavy parasitic capacitance (in old technology), thus dominating the chip area and power consumption. However, the use of nano CMOS technology naturally moderates the limits because shrinking diminishes parasitic capacitances and reduces the silicon area required for the digital control. Recent results show optimum figures-of-merit (FOM) [1]-[3], [11]-[13] with high digitization of the ADC. Therefore, resistive-based DACs become valid solutions even for high-conversion rate. In addition, the use of a resistive DAC provides  $2^N$  reference voltages which can be reused in the various steps of the conversion cycle. Thus, only one DAC is necessary for the Mb/C needs, including the generation of differential references.

Fig. 2 shows the detail of the passive front-end circuit. It uses the DAC voltage in series to the sampled input, stored on  $C_S$ , for minimizing the capacitive load and speeding up the settling. The circuit gives rise at the input of the comparator to the difference between input voltage and DAC output [14] because  $C_S$  behaves as a voltage shifter. The only capacitive load of the DAC consists of the parasitic along the charging path. It includes the parasitic capacitances of  $C_S$ , the switch parasitic, and the input capacitance of the comparator. Such a small capacitive load gives rise to a fast settling, enabling a low-power and small-area resistive DAC design with satisfying settling speed.

#### A. Precision of SAR Cycle

The goal of this design is to optimize ADC speed, power, and linearity in order to find the optimal performance, namely, the lower FOM. The sampling rate is the inverse of the sampling duration plus the SAR cycles, controlled by the analog settling and the digital latency. The *R-C* constant of the DAC (and that of the sampler) determines the settling times; the addition of all of the

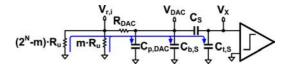

Fig. 3. R-C model of the DAC settling path.

TABLE I

ESTIMATED 6-B ADC PERFORMANCE VERSUS SAR CYCLE PRECISION

| 6-bit ADC                  | 1b/C    | 2b/C    | 3b/C     |

|----------------------------|---------|---------|----------|

| $f_{S,max}$                | 358MS/s | 836MS/s | 1.04GS/s |

| Power @ f <sub>S,max</sub> | 3.27mW  | 3.03mW  | 4.02mW   |

| FOM @ f <sub>S,max</sub>   | 143fJ   | 56.4fJ  | 60.3fJ   |

TABLE II

ESTIMATED 8-B ADC PERFORMANCE VERSUS SAR CYCLE PRECISION

| 8-bit ADC                  | 1b/C    | 2b/C    | 3b/C *  |

|----------------------------|---------|---------|---------|

| $f_{S,max}$                | 109MS/s | 396MS/s | 591MS/s |

| Power @ f <sub>S,max</sub> | 4.02mW  | 4.29mW  | 8.7mW   |

| FOM @ f <sub>S,max</sub>   | 143fJ   | 42.3fJ  | 57.3fJ  |

<sup>\*:</sup> Determine 3, 3 and 2 bits in three subsequent SAR cycles.

gate delay in the digital blocks, including comparator, bit register, and decoder, makes the digital latency. In order to estimate the settling, Fig. 3 represents the R-C model of the DAC and sampling circuit.  $V_{\rm r,i}$  is the reference voltage generated by an N-bit Kelvin ladder with m unit resistor  $R_u$  connected between  $V_{\rm r,i}$  and the ground.  $R_{\rm DAC}$  is the resistance of the enabled DAC switch and  $C_{\rm p,DAC}$  models the additional parasitic capacitances of the DAC's switches.  $C_{\rm p,S}$  is the plates parasitic capacitance of  $C_S$ , including bottom-plate parasitic  $C_{\rm b,S}$  and top-plate parasitic  $C_{\rm t,S}$ . If neglecting the effect of multiple switching on the ladder, the time constant of the DAC settling is

$$\tau = [m \cdot R_u / / (2^N - m) \cdot R_u + R_{DAC}] \cdot (C_{p,DAC} + C_{p,S}).$$

(1)

Since the DAC must settle within half  $V_{\rm LSB}$  to guarantee the linearity, the sampling rate of an N-bit resistive DAC-based SAR ADC [15] with n-bit per step is

$$f_{\rm S}^{-1} = T_{\rm S} = \left(\frac{N}{n} + U\right) \left[\tau \left(N + 1\right) \ln 2 + t_D\right]$$

(2)

where U is the ratio between the duration of the sampling phase and the SAR cycle, and  $t_D$  is the overall digital latency. Although the time constant is not the same in different SAR cycles, the SAR phases have to be uniform without implementing the asynchronous SAR logics. Therefore, in the calculation, the worst time constant is introduced to estimate the maximum clock frequency. The value of the sampling frequency  $f_S$  predicts the speed limitation of the ADC with different resolutions N, and it helps to estimate its FOM as well.

The power consumed by the resistive DAC, comparators, and digital circuits determines the total ADC consumption. The power of the resistive DAC connected between  $V_{\rm REF}$  and ground is given by

$$P_{\text{REF}} = \frac{V_{\text{REF}}^2}{2^{\text{N}} R_{\text{u}}}.$$

(3)

FOM @ fs.

| Resolution (bits)          | 4       | 6       | 8       | 10      |

|----------------------------|---------|---------|---------|---------|

| $f_{S,max}$                | 1.3GS/s | 836MS/s | 396MS/s | 111MS/s |

| Power @ f <sub>S max</sub> | 2.38mW  | 3.03mW  | 4.29mW  | 6.33mW  |

56.4fJ

42.3fJ

TABLE III ESTIMATED PERFORMANCE OF RESISTIVE DAC-BASED 2 B/C SAR ADC

115fJ

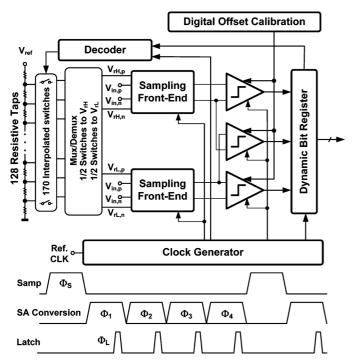

Fig. 4. Proposed ADC architecture and timing diagram.

Also, the power of the digital circuits and comparator are calculated as

$$P_{\text{Digital/Comp}} = f_{\text{CLK}} C_{\text{L}} V_{\text{DD}}^2 \tag{4}$$

where  $f_{\rm CLK}$  is the operation frequency of the circuit and  $C_L$  indicates the overall switched capacitance. In particular, the  $C_L$ of the comparator (including the comparator's load and comparator's intrinsic capacitance) has to be scaled with the ADC resolution, allowing a good noise performance.

The overall DAC resistance is estimated to be 1 k $\Omega$  and  $R_{\rm DAC}$ is 500  $\Omega$ . Each switch's drain or source parasitic capacitance is approximately 0.5 fF, including the proper routing parasitics. Since tens of switches may connect to  $V_{\rm DAC}$  at the same time, the overall capacitance  $C_{\rm p,DAC}$  should be 0.5 fF multiplied by the number of connecting switches. The value of  $C_{p,S}$  should be around 50% of  $C_S$  which can be estimated from the kT/Cnoise. On the other hand,  $t_D$  is close to 250 ps, including the latency in the comparator, bit register, decoder, and intermediate buffers. To estimate the digital power, each gate capacitance is considered to be 5 fF, including the routing capacitance. The total capacitance of the comparator is 80 fF, comprising the extracted capacitance and its MOS-capacitor load for offset calibration as well.

Finally, the above equations estimate the maximum sampling rate and the corresponding power consumption with MATLAB.

55.5fJ

Fig. 5. Implementation of the interpolated sampling front-ends with cross-coupled bootstrapping network.

Accordingly we obtain the maximum achievable FOM, in the case that the ADC achieves its nominal accuracy. Tables I and II summarize the ADC performances for a 6-b and an 8-b ADC with different SAR cycle precision. The ADC speed increases significantly from 1 to 2 b/C, because of two reasons. First, the number of SAR cycles diminishes by 50%. Second, in the 1-b/C structure,  $2^N$  DAC switches connect to a common node of a single sampling circuit, giving rise to a large parasitic capacitance load that slows down the DAC settling. In the 2-b/C structure, the common node of switches is separated by multiple sampling circuits. The capacitive load at each node can be greatly reduced, thus allowing the DAC to settle much faster. Moreover, an interpolation technique (presented later) can be implemented to further reduce the number of switches. The 3-b/C structure still improves the ADC speed, but the enhancement is smaller. Thus, it implies a further doubling of the number of comparators, whose additional side effects are an increase of the comparator's offset calibration hardware, large timing error due to the mismatch of latch phases, and longer latency in the bit register.

The multibit solution benefits the figure of merit and achieves the minimum for 2 bit per cycle. Therefore, the 2-b/C topology exhibits the optimum tradeoff between power and speed.

Moreover, comparing with the 2-b/C SAR structure, another effective way to increase the ADC speed is to use a time-interleaved (T-I) topology. A T-I ADC foresees the multiplication of hardware (and power) and a corresponding increase of speed. However, the FOM of the ADC does not improve or even deteriorates because more power is required by the complex calibra-

Fig. 6. (a) Conventional and (b) proposed interpolated sampling circuits topology in 2-b/cycle SAR structure.

tion circuits that become necessary to reduce the error between channels. On the other hand, a 2-b/C structure not only improves the ADC speed, but also allows DAC reference sharing, thus improving power effectiveness.

#### B. ADC Resolution

The performance of the resistive DAC-based 2-b/C SAR ADC also varies with the ADC resolution. With low resolution, the power is low, while the achievable speed is higher. On the other hand, with high resolution, the speed is lower and larger power is required. In particular, for an ADC resolution of 10 b, which exceeds the dynamic comparator's accuracy [16], a preamplifier has to be inserted before the comparator to guarantee the ADC precision, with the power of a single-stage preamplifier estimated in [15]. However, a high-speed preamplifier is quite power-thirsty and it may greatly degrade the ADC efficiency. Therefore, it is necessary to examine the ADC's performance in terms of power and speed, for different ADC resolutions, in order to determine the optimum efficiency point. Finally, (1)–(4) are supposed to achieve full resolution, leading to the results summarized in Table III, obtained with the same capacitor/resistor setting of Section II-A. Thus, a conclusion can be drawn; with a resistive DAC-based 2-b/C SAR structure, a moderate specification of 8 b achieves the best FOM.

#### III. CIRCUIT IMPLEMENTATION

Fig. 4 shows the architecture and timing diagram of the implemented 8-b 400-MS/s resistive DAC-based 2-b/C SAR ADC. The digital decoder controls 170 switches to provide two differential reference voltages,  $V_{\rm rH}$  and  $V_{\rm rL}$ . Two sampling frontends generate the difference between the input and the references. The differential signals serve a three-level interpolation network with three fast comparators [17], [18]. An on-chip foreground offset calibration circuit [19] minimizes the offset of the comparators. The scheme adjusts the comparators offset with a digital controlled MOS capacitance located at the comparators' outputs. The use of interpolation reduces the number of switches and decoders, thus diminishing consumed power and area. An on-chip clock generator provides the timing phases for the sampling circuit, comparator, bit register, and decoder, with a master input clock equal to the sampling rate.

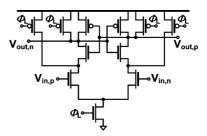

# A. Interpolated Sampling Circuits With Cross-Coupled Bootstrapping Network

Fig. 5 shows the interpolated sampling circuits, where capacitors  $C_S$  sample the input signal during the sampling phase  $\Phi_S$  and hold it for the entire conversion period. The use of a resistive DAC enables a very fast settling with a relatively small dynamic and affordable power, since it is required to charge only the parasitic capacitances. The input range is defined as 1.2 V, peak-to-peak, differential, with a common-mode voltage of 0.3 V equal to the common mode of the reference voltage.  $V_{\rm CM}$  is 0.6 V and defines the input common mode of the comparator.

Comparing with the conventional sampling approach in Fig. 6(a), interpolation is able to reduce the number of sampling circuits as shown in Fig. 6(b), implying a saving of the sampling power. An important feature of this structure is the reduction of the number of reference-selecting switches by 1/3, as well as the switches' control logics. Moreover, because the difference of the two provided DAC reference voltages (V<sub>rH,p</sub> and  $V_{\rm rL,p}$ ) in the last SAR cycle has been doubled to be  $2V_{\rm LSB}$ , the number of taps in the resistive ladder can be consequently halved (from 256 to 128). As shown in Fig. 6(b), the middle comparator takes the output voltages from the upper and lower sampling networks, which effectively interpolate the extra reference such that a 128-tap DAC is used in this 8-b ADC. In addition, the resolution of the implemented resistive DAC is still 8 b, although it includes only 128 taps. The benefit of tap reduction derives directly from the reduction of the physical length of the resistive DAC, because the minimum length of the unit resistor is limited. Further details will be shown in the reference DAC implementation.

Kickback noise is also an important issue of comparator design. In order to balance this dynamic error, as well as the load of the sampling circuit, two extra dummy comparators are utilized. With identical clock phase and supply voltage, the dummy comparators inject the same amount of charge back to the sampling circuit, as the three functional comparators. When comparators start latching, the two differential outputs of the sampling circuit drop the same amount of voltage because of the equalized kickback. At the end of each latch phase, the sampling circuit will wait for the recovery of kickback before starting the next SAR cycle.

Bootstrapping of the sampling switch makes almost constant the clock feedthrough [21], and the voltage driving the switch,

Fig. 7. Switching operation of the reference DAC.

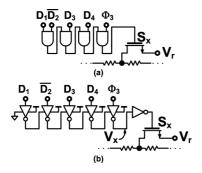

Fig. 8. Different implementations of the decoder unit in the third conversion cycle by (a) AND/NAND gates and (b) cascaded inverters.

$V_{\rm GS}$ , is almost constant. However, since the rising edge of the bootstrapped clock phase depends on  $V_{\rm in}$ , there is a second-order signal-dependent clock feedthrough term. In this design, it is alleviated by the cross-connected capacitance  $C_C$ . The value of those capacitances matches the parasitic  $C_{\rm gd}$  of  $M_{\rm SW}$ .

Comparator offset is a key error term which is attenuated by a foreground digital calibration in this design. When the offset calibration is enabled the differential input of the comparator is shorted to  $V_{\rm CM}$  by nMOS switches controlled by  $\Phi_{\rm cal}$ , as shown in Fig. 5. Subsequently, the calibration logics (presented in offset calibration section), will detect the comparator's output and will unbalance the load of the comparator to neutralize its offset. Once the calibration is over,  $\Phi_{\rm cal}$  will be low and the comparators will sense the output of the sampling circuit to initialize normal A/D conversion.

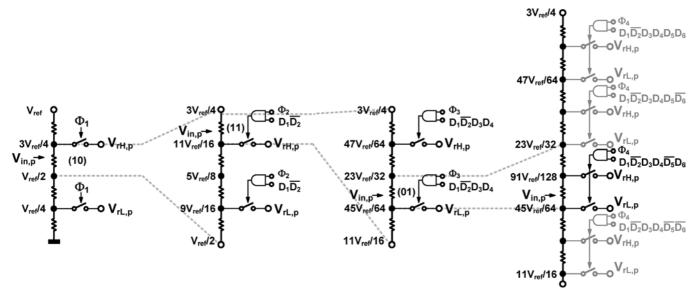

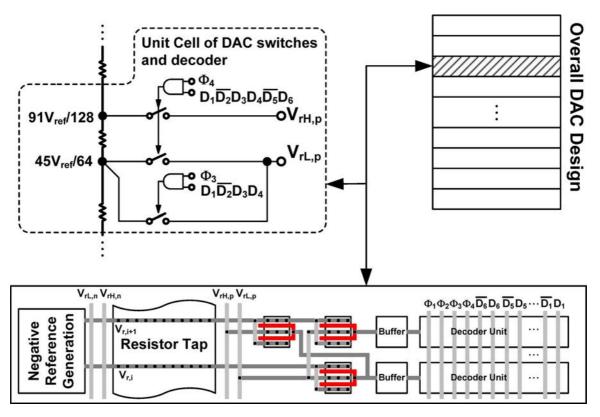

#### B. Reference DAC

The 128 taps resistive DAC with a total resistance of 750  $\Omega$  is connected between  $V_{\rm ref}$  and ground.  $V_{\rm ref}$  is at midsupply to allow the use of single nMOS as DAC switches. Because of the lower threshold voltage of nMOS transistors, the choice enables rapid settling having minimum parasitic capacitances. Fig. 7 highlights, as an example of a switching operation, the selection of the positive reference voltage of the resistive DAC.

Fig. 9. Implementation of comparator offset calibration.

Fig. 10. Circuit implementation of dynamic comparator.

The selection to obtain the complementary reference is similar, where  $V_{\rm rH,n}$  (or  $V_{\rm rL,n})=V_{\rm ref}-V_{\rm rH,p}$  (or  $V_{\rm rL,p}).$  Each side of the reference generation includes 170 switches (340 switches for overall differential DAC implementation) which have been reduced by 1/3 from the original number of 255, due to the interpolation. The 106 decoder units with the AND function are laid out together with the related switch. The inputs of the decoders are the corresponding approximation phases and the determined digital bits. The ADC approximates the input in four steps. The first step activates the switches that provide  $3V_{\rm ref}/4$  and  $V_{\rm ref}/4$  to  $V_{\rm rH,p}$  and  $V_{\rm rL,p}$ . The following steps are similar but the control exploits the determined digital bits. Since the difference of  $V_{\rm rH,p}$  and  $V_{\rm rL,p}$  of the last step is twice the value of  $V_{\rm LSB}$  ( $V_{\rm ref}/2^8$ ), only 128 resistive taps of the DAC

Fig. 11. Layout implementation of DAC unit cell.

are required. Reducing the taps by half saves significant area and alleviates the gradient effect in the DAC. In addition, the two active switches in the last step are physically close to each other in order to share one decoder, thus achieving power and area optimization.

#### C. Digital Decoder

Fig. 8(a) shows an AND gates structure suitable for decoding the already determined bits and driving one of the selection switches. This design uses the more effective method of Fig. 8(b) made by a special configuration of inverters. The figure shows the 1011 selection control, possibly used at the third step of conversion. The cascade uses the output of an inverter as ground connection of the subsequent one. The decoder design realizes the same function but reduces by approximately half the number of the transistors, saving a considerable amount of power. The operation, similar to pass transistor logic, requires all zeros at the beginning of the conversion cycle for setting the outputs  $V_{\rm X}$  at  $V_{\rm DD}$ . The operation is quite fast because the speed only depends on the transition time of the last inverter, while the controls of others are already set.

# D. Offset Calibration

Fig. 9 shows the topology [19] of the offset calibration, which is realized by a variable capacitor added to the output of the comparator [20], as shown in Fig. 10. Similar to the previous calibration scheme [18], the comparator offset is compensated by unbalancing the dynamic response of the comparator. The variable capacitor is implemented by a pMOS capacitor, where the gate voltage is controlled by a multiplexer selecting the reference voltage from a resistive ladder. The multiplexer,

which is a tree of switches, gives rise to a calibration ramp. The counter changes the calibration capacitor until the crossing of the threshold. Though the ladder exhibits static current, it has been demonstrated to be low because calibration speed is not necessary as fast as in the normal A/D conversion. The additional calibration slightly attenuates the comparator operation speed but to a much lesser extent than the calibration method used in [18] that needs  $2^N$  capacitors for N-bit calibration resolution. Fig. 9 also illustrates the timing diagram of the offset calibration, which is enabled off-chip. Once the calibration is triggered,  $\Phi_{\rm cal}$  goes high to calibrate the three comparators sequentially. Once calibration is over,  $\Phi_{\rm cal}$  returns to low and the ADC starts conversion.

#### IV. LAYOUT CONSIDERATIONS

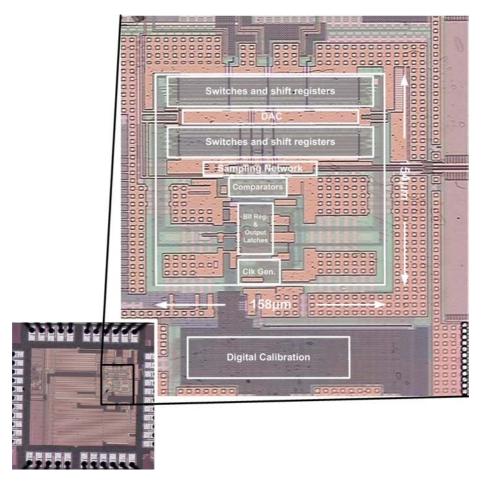

The SAR ADC prototype is laid out in a 65-nm single-poly, seven-metal CMOS with low-threshold option (the value of  $V_{\rm TH}$  is approximately 280 mV). One of the most important issues of this SAR ADC is that its approximation loop operates at an extremely high speed: 2 GHz. A compact layout is therefore vital to limit the propagation delay on the metal routings. Special attention is paid to the layout of the resistive DAC, together with its switches and digital decoder, which constitutes the most complex block in the ADC design, since it includes 212 decoder units and 340 controlled DAC switches (for differential reference voltage generation). Indeed, the ADC area is good for more than a general assessment of the ADC performance; a small area design with less parasitic and less gradient enables better performance in both power and speed [22].

Fig. 12. Chip micrograph.

Tens of unit cells make the DAC and decoder, each of them consisting of two resistor taps and switches. The small width of the rectangular cells minimizes the gradient error of the resistive unity elements. Fig. 11 refers to positive reference generation. The layout for negative reference generation is similar and symmetrical. The switches are implemented with two-finger configuration for minimizing the drain parasitic, load of  $V_{\rm rH,p}$  and  $V_{\rm rL,p}$ . The area of the overall DAC layout is 60  $\mu m \times$  140  $\mu m$ .

### V. MEASUREMENT RESULTS

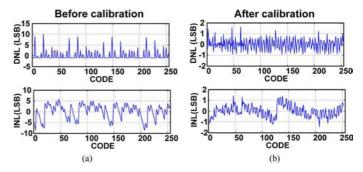

Fig. 12 shows the micrograph of the fabricated prototype design. The ADC core occupies  $154 \times 158~\mu\text{m}^2$ , in which the on-chip digital calibration is  $35 \times 117~\mu\text{m}^2$ . The differential nonlinearity (DNL) and integral nonlinearity (INL) measured with either a voltage ramp or a low-frequency sinusoidal wave at the input [23] give rise to the static performance. Fig. 13(a) shows that, before calibration the measured DNL and INL are -1/+10.2~LSB and -8.6/+5.9~LSB at 400-MS/s conversion rate. With calibration and the same sampling frequency, the nonlinearities are greatly reduced. The DNL and INL become -0.9/+1.6~LSB and -1.5/+1.4~LSB, as illustrated in Fig. 13(b).

A single tone to the inputs and the recorded code stream measures the dynamic performance of the prototype ADC, with output decimated by 25 times. Fig. 14(a) shows the FFT spectrum for a 1.2  $V_{\rm p-p}$  1.9 MHz input signal. The SNDR and SFDR are 44.4 dB and 56.4 dB, respectively. Fig. 14(b) presents

Fig. 13. Measured DNL and INL (a) without and (b) with comparator offset calibration at 400 MS/s.

the output FFT spectrum with input near Nyquist; the SNDR and SFDR are 40.1 and 52.4 dB, respectively. Fig. 14(c) illustrates the measured peak at different sampling rates. The SNDR versus input frequency is plotted in Fig. 14(d) with two different sampling rates. With 400-MS/s sampling frequency and 1.2-V supply, the SNDR is above 40 dB; with 250-MS/s sampling frequency and 1-V supply, the SNDR is higher and above 44 dB. The total dissipated power of the prototype ADC at 400 MS/s is 4 mW from a 1.2-V supply; 0.49 mW (12% of the total) is used for the resistive DAC. Operating at 250 MS/s from 1-V supply, the ADC requires only 1.8-mW power and the DAC uses 0.43 mW (24%) of the total. Table IV summarizes the performance of the proposed ADC. It achieves a very high power

Fig. 14. Measured dynamic performance. (a) FFT spectrum at 2-MHz input (output decimated by 25). (b) FFT spectrum at Nyquist input (output decimated by 25). (c) SNDR versus conversion rate. (d) SNDR versus input frequency.

| Specifications                               | This Work |      | ISSCC'09 | ISSCC'08 | ISSCC'07  | VLSI'11    | CICC'10 |

|----------------------------------------------|-----------|------|----------|----------|-----------|------------|---------|

|                                              |           |      | [24]     | [25]     | [26]      | [27        | [28]    |

| Architecture                                 | SAR       |      | TI-SAR   | 2-Step   | Pipelined | TI-Counter | TI-SAR  |

| Technology (nm)                              | 65        |      | 130      | 90       | 180       | 130        | 65      |

| Resolution (bits)                            |           | 3    | 8        | 8        | 8         | 8          | 10      |

| Sampling Rate (MS/s)                         | 400       | 250  | 600      | 300      | 200       | 500        | 204     |

| Supply Voltage (V)                           | 1.2       | 1    | 1.2      | 1.2      | 1.8       | 1.2        | 1       |

| SNDR (dB)                                    | 44.5      | 46.7 | 47       | 46.1     | 40.3      | 44.6       | 55.2    |

| Power (mW)                                   | 4         | 1.8  | 30       | 34       | 8.5       | 26         | 9.15    |

| FOM1 @ Low f <sub>in</sub> (fJ/Convstep)     | 73        | 42   | 208      | 680      | -         | 350        | 95.4    |

| FOM2 @ Nyquist f <sub>in</sub> (fJ/Convstep) | 117       | 60   | 340      | 780      | 510       | 380        | 130     |

| Active Area (mm²)                            | 0.028     |      | 1.1      | 0.29     | 0.05      | 0.55       | 0.22    |

TABLE IV

PERFORMANCE BENCHMARK WITH STATE-OF-THE-ART DESIGNS

efficiency and compact area when compared with the state of the art with similar specifications. It is also faster than the previous single-channel SAR ADC with  $\rm SNDR > 40~dB$  [29].

#### VI. CONCLUSION

This paper presents an 8-b 400-MS/s ADC with resistive DAC-based 2-b/C SAR structure, which has been demonstrated to achieve good efficiency at high conversion speed. Several effective solutions at the circuit and layout level, like the interpolated sampling circuits and cascaded-inverter based decoder, optimize the power/area cost of the ADC. A cross-coupled bootstrapping network and offset calibration enhance the accuracy. The proposed ADC is a valuable solution to solve

the stringent tradeoff among power, speed, and resolution and achieves a FOM of 73 fJ/conversion-step at a 400-MS/s conversion rate. Comparing with capacitive SAR ADC, this ADC topology my lose effectiveness at high resolution level, but it extends the application range of SAR ADCs in speed. It is also believed to be a good approach that might scale well into future technologies.

### REFERENCES

[1] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, and B. Nauta, "A 1.9  $\mu W$  4.4 fJ/conversion-step 10 b 1 MS/s charge-redistribution ADC," in *ISSCC Dig. Tech. Papers*, Feb. 2008, pp. 244–245.

- [2] J. Craninckx and G. Van der Plas, "A 65 fJ/conversion-step 0-to-50 Ms/s 0-to-0.7 mW 9 b charge-sharing SAR ADC in 90 nm digital CMOS," in *ISSCC Dig. Tech. Papers*, Feb. 2007, pp. 246–247.

- [3] M. Yoshioka, K. Ishikawa, and T. Takayama, "A 10 b 50 MS/s 820  $\mu$ W SAR ADC with on-chip digital calibration," in *ISSCC Dig. Tech. Papers*, Feb. 2010, pp. 384–385.

- [5] Z. Cao, S. Yan, and Y. Li, "A 32 mW 1.25 GS/s 6 b 2 b/step SAR ADC in 0.13  $\mu$ m CMOS," in *ISSCC Dig. Tech. Papers*, Feb. 2008, pp. 542–543.

- [6] H. Wei, C.-H. Chan, U.-F. Chio, S.-W. Sin, S.-P. U, R. Martins, and F. Maloberti, "0.024 mm<sup>2</sup> 8 b 400 MS/s SAR ADC with 2 b/cycle and resistive DAC in 65 nm CMOS," in *ISSCC Dig. Tech. Papers*, Feb. 2011, pp. 188–189.

- [7] B. Razavi, Principles of Data Conversion System Design. New York: IEEE Press, 1995.

- [8] T. Yamamoto, S. Gotoh, T. Takahashi, K. Irie, and K. Ohshima, "A mixed-signal 0.18-μm CMOS SoC for DVD systems with 432-Msample/s PRML read channel and 16-Mb embedded DRAM," *IEEE J. Solid-State Circuits*, vol. 36, no. 11, pp. 1785–1794, Nov. 2001

- [9] K. Nagaraj, D. Martin, M. Wolfe, R. Chattopadhyay, S. Pavan, J. Cancio, and T. Viswanathan, "A dual-mode 700 MSPS/6 bit 200 MSPS/7 bit A/D converter in a 0.25 μm digital CMOS process," *IEEE J. Solid-State Circuits*, vol. 35, no. 12, pp. 1760–1768, Dec. 2000.

- [10] A. R. Hamade, "A single chip all-MOS 8-bit A/D converter," *IEEE J. Solid-State Circuits*, vol. SSC-13, no. 6, pp. 785–791, Dec. 1978.

- [11] B. Murmann, "ADC Performance Survey 1997–2011." [Online]. Available: http://www.stanford.edu/~murmann/adcsurvey.html

- [12] G. Van der Plas and B. Verbruggen, "A 150 MS/s 133 μW 7 b ADC in 90 nm digital CMOS using a comparator-based asynchronous binary-search sub-ADC," in *ISSCC Dig. Tech. Papers*, Feb. 2008, pp. 242–243.

- [13] C. Liu, S. Chang, G. Huang, Y. Lin, C. Huang, C. Huang, L. Bu, and C. Tsai, "A 10 b 100 MS/s 1.13 mW SAR ADC with binary-scaled error compensation," in *ISSCC Dig. Tech. Papers*, Feb. 2010, pp. 386–387.

- [14] G. Huang, C. Liu, Y. Lin, and S. Chang, "A 10-bit 12-MS/s successive approximation ADC with 1.2-pF input capacitance," in *Proc. ASSCC*, Nov. 2009, pp. 157–160.

- [15] B. P. Ginsburg and A. P. Chandrakasan, "Dual time-interleaved successive approximation register ADCs for an ultra-wideband receiver," IEEE J. Solid-State Cicuits, vol. 42, no. 2, pp. 247–257, Feb. 2007.

- [16] P. Nuzzo et al., "Noise analysis of regenerative comparator for reconfigurable ADC architecture," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 6, pp. 1441–1454, Jul. 2008.

- [17] B. Verbruggen et al., "A 2.2 mW 5 b 1.75 GS/s folding flash ADC in 90 nm digital CMOS," in ISSCC Dig. Tech. Papers, Feb. 2008, pp. 252–253.

- [18] G. Van der Plas, S. Decoutere, and S. Donnay, "A 0.16 pJ/conversionstep 2.5 mW 1.25 GS/s 4 b ADC in a 90 nm digital CMOS process," in *ISSCC Dig. Tech. Papers*, Feb. 2006.

- [19] C. Chan, Y. Zhu, U. Chio, S. Sin, S. U, and R. P. Martins, "A voltage-controlled capacitance offset calibration technique for high resolution dynamic comparator," in *Proc. Int. SoC Design Conf.*, Nov. 2009, pp. 392–395.

- [20] T. B. Cho and P. R. Gray, "A 10 b, 20 Msample/s, 35 mW pipeline A/D converter," *IEEE J. Solid-State Circuits*, vol. 30, no. 3, pp. 166–172, Mar. 1995.

- [21] Steensgaard, "Bootstrapped low-voltage analog switches," in *Proc. IEEE Int. Symp. Circuits Syst.*, 1999, vol. 2, pp. 29–32.

- [22] A. Verma and B. Razavi, "A 10 b 500 MHz 55 mW CMOS ADC," in ISSCC Dig. Tech. Papers, Feb. 2009, pp. 84–85.

- [23] J. Doernberg, H. Lee, and D. Hodges, "Full-speed testing of A/D converters," *IEEE J. Solid-State Circuits*, vol. SSC-19, no. 12, pp. 820–827, Dec. 1984.

- [24] W. Liu *et al.*, "A 600 MS/s 30 mW 0.13  $\mu$ m CMOS ADC array achieving Over 60 dB SFDR with adaptive digital equalization," in *ISSCC Dig. Tech. Papers*, Feb. 2009, pp. 82–83.

- [25] Y. Shimizu et al., "A split-load interpolation-amplifier-array 300 MS/s 8 b subranging ADC in 90 nm CMOS," ISSCC Dig. Tech. Papers, pp. 552–553, Feb. 2008.

- [26] L. Brooks et al., "A zero-crossing-based 8 b 200 MSs pipelined ADC," ISSCC Dig. Tech. Papers, pp. 460–461, Feb. 2007.

- [27] S. Danesh et al., "A rReconfigurable 1 GSps to 250 MSps, 7-bit to 9-bit highly time-interleaved counter ADC in 0.13 μm CMOS," in Proc. IEEE Symp. VLSI Circuits, Jun. 2011, pp. 268–269.

- [28] Y. D. Jeon et al., "A 9.15 mW 0.22 mm<sup>2</sup> 10 b 204 MS/s pipelined SAR ADC in 65 nm CMOS," in Proc. IEEE Custom Integr. Circuits Conf., Sep. 2010, pp. 1–4.

- [29] C. Liu, S. Chang, G. Huang, Y. Lin, C. Huang, C. Huang, L. Bu, and C. Tsai, "A 10 b 100 MS/s 1.13 mW SAR ADC with binary-scaled error compensation," in *ISSCC Dig. Tech. Papers*, Feb. 2010, pp. 386–387.

**Hegong Wei** (S'05–M'10) received the B.Sc., M.Sc., and Ph.D. degrees (with honors) in electrical and electronics engineering from the University of Macau, Macao, China, in 2006, 2008, and 2011, respectively.

He was a Project Leader with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macao, China. He is currently a Postdoctoral Fellow with the Circuit Communication Laboratory, University of California, Los Angeles. His research interests include high-speed and high-perfor-

mance data converters and mixed-signal circuits design and has authored and coauthored over 20 technical journals and conference papers in this field.

Dr. Wei received the Silk-Road Award at ISSCC 2011.

**Chi-Hang Chan** (S'12) received the B.Sc. degree from the University of Washington, Seattle. He is currently working toward the M.S. degree at the University of Macau, Macao, China.

He was an Intern with Chip Idea Macau (now also with Synopsys) during his undergraduate work. He is currently with the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macao, China. His research focuses mainly on gigahertz-range ADCs with low and moderate resolution, comparators, dynamic circuit design, and

mixed-signal layout consideration.

**U-Fat Chio** received the B.Sc. degree in electrical engineering and M.Sc. degree from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2002 and 2004, respectively, and the Ph.D. degree from the University of Macau, Macao, China, in 2012.

From 2004 to 2005, he was with DenMOS Technology Inc., Hsinchu, Taiwan. His research interest is high-speed analog-to-digital converters and power management circuit designs.

Sai-Weng Sin (S'98–M'06) received the B.Sc., M.Sc., and Ph.D. degrees (with highest honor) in electrical and electronics engineering from the University of Macau, Macao, China, in 2001, 2003, and 2008, respectively.

He is currently an Assistant Professor with the Faculty of Science and Technology, University of Macau, Macao, China, and is the Coordinator of the Data Conversion and Signal Processing (DCSP) Research Line in State-Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau. He

has authored one book, entitled *Generalized Low-Voltage Circuit Techniques* for Very High-Speed Time-Interleaved Analog-to-Digital Converters (Springer, 2010) and over 70 technical journals and conference papers in the field of high-performance data converters and analog mixed-signal integrated circuits.

Dr. Sin is/was a member of the Technical Program Committee of IEEE Sensors 2011 and IEEE RFIT 2011–2012 Conference, Review Committee Member of PrimeAsia 2009 Conference, Technical Program and Organization Committee of the 2004 IEEJ AVLSI Workshop, as well as the Special Session Co-Chair and Technical Program Committee Member of 2008 IEEE APCCAS Conference. He is currently the Secretary of the IEEE Solid-State Circuits Society (SSCS) Macau Chapter and IEEE Macau CAS/COM Joint Chapter.

He was the corecipient of the 2011 ISSCC Silk Road Award, Student Design Contest winner in A-SSCC 2011, and the 2011 State Science and Technology Progress Award (second-class), China.

Seng-Pan U (S'94–M'00–SM'05) received the B.Sc. and M.Sc. degrees from the University of Macau, Macao, China, in 1991 and 1997, respectively, and the joint Ph.D. degree (with highest honor) from the University of Macau and the Instituto Superior Técnico, Universidade Técnica de Lisboa (IST/UTL), Lisbon, Portugal, in 2002. His doctoral work focused on the field of high-speed analog IC design.

He has been with the Department of Electrical and Electronic Engineering, Faculty of Science and Tech-

nology (FST), University of Macau, Macao, China, since 1994, where he is currently a Professor and Deputy Director of State-Key Laboratory of Analog and Mixed-Signal VLSI. During 1999-2001, he was also on leave to the Integrated CAS Group, Center of Microsystems, IST/UTL, as a Visiting Research Fellow. In 2001, he cofounded Chipidea Microelectronics Ltd., Macao, and he was an Engineering Director and, since 2003, the corporate Vice-President of IP Operations Asia Pacific and site General Manager of the company for devoting in advanced analog and mixed-signal semiconductor ip (SIP) product development. Chipidea was acquired in May 2009 by Synopsys Inc., where he is currently the corporate Senior Analog Design Manager and Site General Manager. He has authored and coauthored more than 120 scientific papers for journals and conferences. He holds five U.S. patents and has coauthored Design of Very High-Frequency Multirate SC Circuits-Extending the Boundaries of CMOS AFE Filtering (Springer, 2005), Analog-Baseband Architectures and Circuits for Multistandard and Low-Voltage Wireless Transceivers (Springer, 2007), and Generalized Low-Voltage Circuit Techniques for Very High-Speed TI ADCs (Springer, 2010).

Dr. U received various scholarship and R&D grants, along with over 20 research and academic/teaching awards. He is also the advisor for over 20 international student paper award recipient. He has also received, for the first time from the University of Macau, the Scientific and Technological Innovation Award of Ho Leung Ho Lee Foundation in 2010 and The State Scientific and Technological Progress Award in 2011. In recognition of his contribution to high-technology research and industrial development in Macau, he was awarded by Macau SAR government the Honorary Title of Value in 2010. He is the Industrial Relationship Officer of IEEE Macau Section, the Chairman of the IEEE Macau CAS/COMM chapter, and the founding Chairman of the IEEE Macau Solid-State Circuits Chapter. He has been with technical review committee of various international scientific journals and conferences for many years. He was the chairman of the local organization committee of IEEJ AVL-SIWS'04, the Technical Program Co-Chair of IEEE APCCAS'08, ICICS'09. and PRIMEAsia'11. He is currently a member of the Technical Program Committee of RFIT, VLSI-DAT, and A-SSCC.

Rui Paulo Martins (M'88–SM'99–F'08) was born on April 30, 1957. He received the B.Sc. M.Sc., Ph.D., and *Habilitation* for Full-Professor in electrical engineering and computers from the Department of Electrical and Computer Engineering, Instituto Superior Técnico (IST), Technical University of Lisbon, Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

He has been with the Department of Electrical and Computer Engineering (DECE)/IST, Technical University (TU) of Lisbon, Lisbon, Portugal, since Oc-

tober 1980. Since 1992, he has been on leave from IST, TU of Lisbon, and is with the Department of Electrical and Computer Engineering, Faculty of Science and Technology (FST), University of Macau, Macao, China, where he has been a Full Professor since 1998. In FST, he was the Dean of the Faculty from 1994 to 1997 and he has been Vice-Rector of the University of Macau since 1997. Since September 2008, after the reform of the UM Charter, he was nom-

inated after open international recruitment as Vice-Rector (Research) until August 31, 2013. Within the scope of his teaching and research activities he has taught 21 bachelor and master courses and has supervised (or co-supervised) 26 theses, Ph.D. (11) and Masters (15). He has published 12 books, coauthoring five and coediting seven, plus five book chapters, 237 refereed papers, as well as 70 other academic works. He has coauthored four U.S. patents with another six pending. He created the Analog and Mixed-Signal VLSI Research Laboratory of UM (http://www.fst.umac.mo/en/lab/ans\_vlsi/website/index.html) elevated in January 2011 to State Key Lab of China (the first in Engineering in Macao), as its Founding Director. He is the financial manager, recognized by EU, of a Jean Monnet Chair in "EU Law – Facing the Constitution and Governance Challenges in the Era of Globalization", unique in the universities from HK and Macao, for the period 2007 to 2012.

Prof. Rui Martins was the Founding Chairman of the IEEE Macau Section from 2003 to 2005 and of the IEEE Macau Joint-Chapter on Circuits And Systems (CAS)/Communications (COM) from 2005 to 2008 [2009 World Chapter of the Year of the IEEE Circuits and Systems (CAS) Society]. He was the General Chair of the 2008 IEEE Asia-Pacific Conference on Circuits and Systems and was the Vice-President for the Region 10 (Asia, Australia, the Pacific) of the IEEE CAS Society, for the period of 2009 to 2011. He is now the Vice-President (World) Regional Activities and Membership of the IEEE CAS Society for the period 2012 to 2013. He has been an associate editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS since 2010 and until 2013. He was the recipient of two government decorations: the Medal of Professional Merit from Macao Government (Portuguese Administration) in 1999, and the Honorary Title of Value from Macao SAR Government (Chinese Administration) in 2001. In July 2010 was elected, unanimously, as Corresponding Member of the Portuguese Academy of Sciences (in Lisbon), being the only Portuguese Academician living in Asia.

Franco Maloberti (F'96) received the Laurea degree in physics (*summa cum laude*) from the University of Parma, Parma, Italy, in 1968, and the Dr. Honoris Causa degree in electronics from Inaoe, Puebla, Mexico, in 1996.

He was a Visiting Professor with ETH-PEL, Zurich, Switzerland, in 1993 and with EPFL-LEG, Lausanne, Switzerland, in 2004. He was a Professor of Microelectronics and Head of the Micro Integrated Systems Group University of Pavia, Pavia, Italy, the TI/J.Kilby Analog Engineering Chair Pro-

fessor with the Texas A&M University, and the Distinguished Microelectronic Chair Professor with University of Texas at Dallas. Currently, he is a Professor with the University of Pavia, Pavia, Italy, and Honorary Professor with the University of Macau, Macao, China. His professional expertise is in the design, analysis, and characterization of integrated circuits and analog digital applications, mainly in the areas of switched capacitor circuits, data converters, interfaces for telecommunication and sensor systems, and portable power management. He has authored and coauthored more than 470 paper and five books and holds 30 patents. He has been responsible for many research programs including ten ESPRIT projects and served the European Commission in many European Initiatives. He served the Academy of Finland on the assessment of electronic research. He served the National Research Council of Portugal for the research activity assessment of Portuguese Universities. He was a Member of the Advisory Board of INESC-Lisbon, Portugal. He is the Chairman of the Academic Committee of the Microelectronics Key Lab., Macau, China.

Dr. Maloberti was Vice President Region 8 of the IEEE Circuits and Systems (CAS) Society (1995–1997), an associate editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS, President of the IEEE Sensor Council (2002–2003), IEEE CAS BoG member (2003–2005), and VP Publications IEEE CAS (2007–2008). He was a Distinguished Lecturer of the IEEE Solid-State Circuits (SSC) Society (2009–2010) and presently is Distinguished Lecturer of the IEEE CAS Society. He received the 1999 IEEE CAS Society Meritorious Service Award, the 2000 CAS Society Golden Jubilee Medal, and the IEEE Millennium Medal. He was corecipient of the 1996 IEE Fleming Premium, the ESSCIRC 2007 Best Paper Award, and the IEEJ Workshop 2007 and 2010 Best Paper Award.